Hi TI Experts,

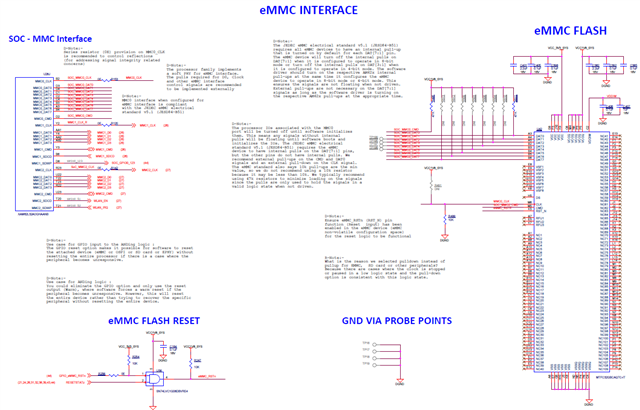

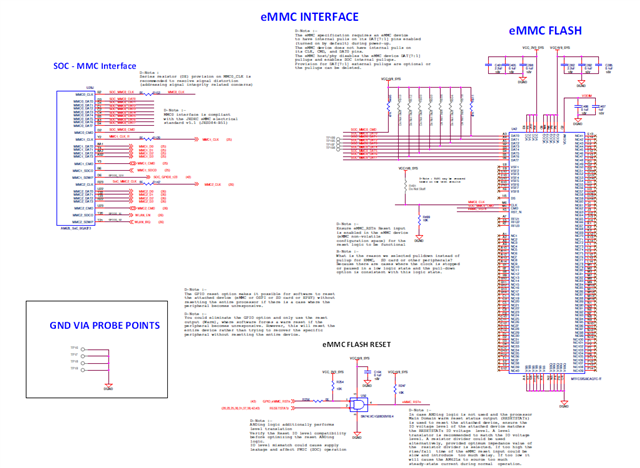

Is there a list of design recommendations or commonly observed errors for eMMC MEMORY Interface during Custom board hardware design?

Below are some common queries i have

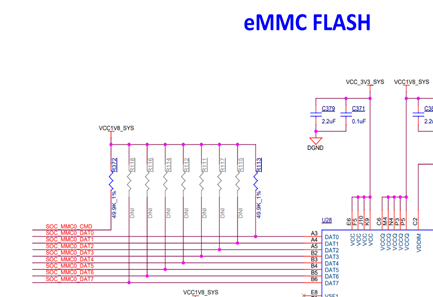

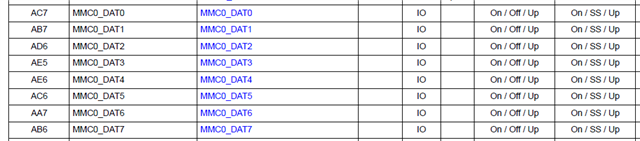

1. Pullup recommendation

2. Power supply and Sequencing

3. Series resistor for eMMC clock output from the processor

4.Series resistors for Data and command signals

5. Calibration resistor

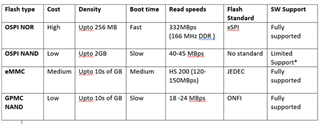

6. Alternate Part recommendations

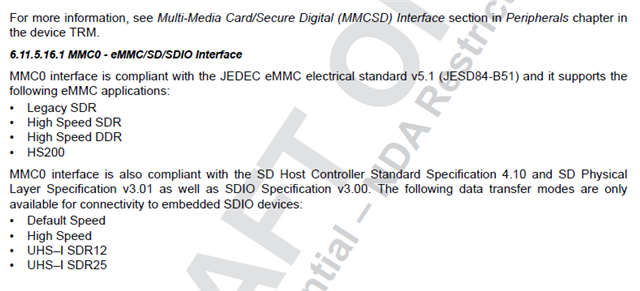

7. Are these recommendations valid for AM64x

8. Is the reset ANDing logic for the device required and any recommendations?

9. What is the default drive strength and can the drive strength be controlled?

Note:

Application Report TDA4 Flashing Techniques