Hi Rahul,

I have been discusing this issue on other thread. You ask for a new post for easy track. Here is this new post.

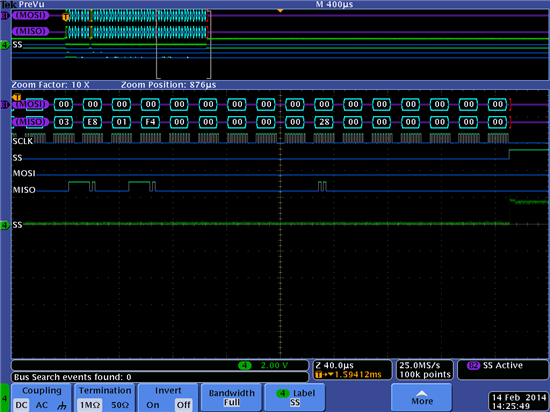

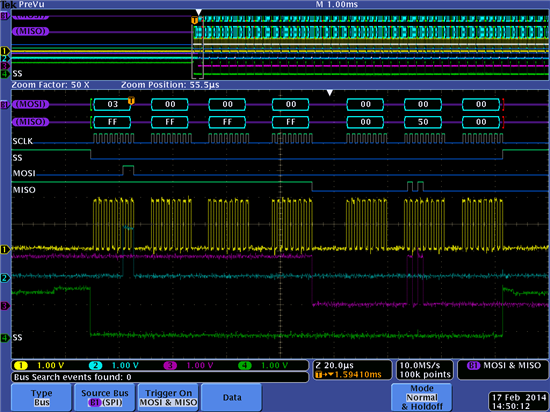

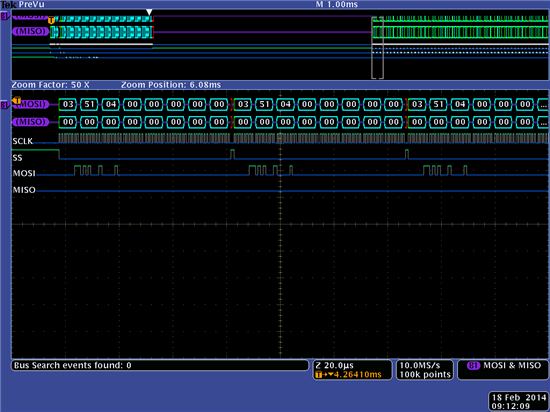

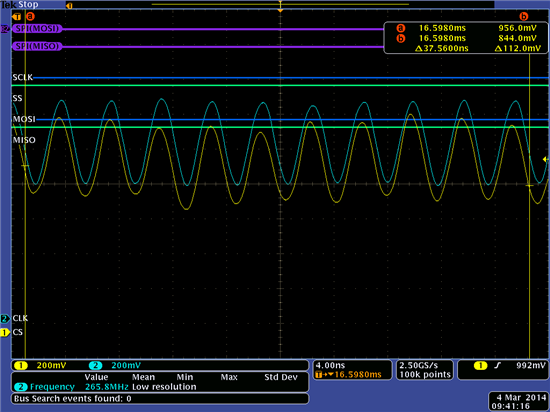

The RBL only reads the 40 bytes (high lighted) then stops. What might be the problem? I am attaching the scope capture for your inspection. That includes analog display for Chip Select.

Thank you.

Regards,

Steve