Tool/software: Linux

Hello,

We are stuck when trying to get to work our PCIe interface.

We designed a carrier board for de phytec AM5728 SOM (https://phytec.com/products/system-on-modules/phycore/am57x/)

In either TI AM5728 SDK or Phytech SDK, the two lane PCIe interfaces are routed to one PCIe connector. Given our need of two different PCIe cards, our carrier board has two different PCIe connectors, each one single lane.

In theory, routing TX0/RX0 to one connector and TX1/RX1 to another connector should do the work. Besides there is a 3xOutput PCIe Gen2 compliant clock generator which generates an appropriate clock to the PCIe cards and to the AM5728. There are also x2 PWR_GD signals, x2 Wake and 2x presence signals.

The problem that we have is that the link, at start time, is not usually linked. Sometimes it is but generally speaking does not succeded.

Here some images of my problem:

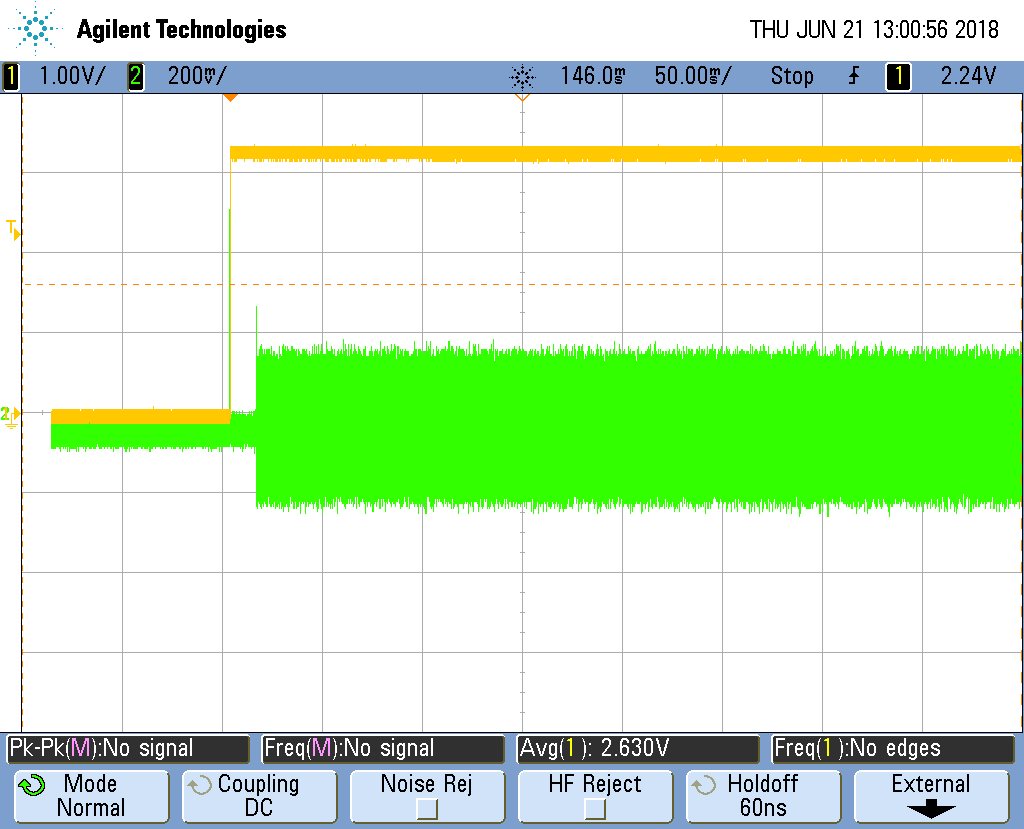

- Yellow colour is the PWR_GD signal from the CPU to the PCIe card.

- Green is TX0_P (from CPU to one of my PCIe connectors where a PCIe card is inserted). .Oscilloscope measurements are single ended

We can see that after PWR_GD goes high, there is some information exchange that continues when the link is established but stops when it fails. Furthermore I see that the electrical levels in this negotiation are not constant which really concerns me.

Example of my card (where each lane is routed to one PCIe connector) when link fails:

Example of my card when link succeed

Example of evaluation kit (where the two lanes are routed to one PCIe connector)

Here we see that electrical levels are constant and there is no initial burst information. It is continuous.

Do you have any hint about what the problem could be?

Many thanks in advance.

Regards,