Other Parts Discussed in Thread: TLK105, TLK106

Tool/software: TI-RTOS

Dear TI team,

I need to verify the HW design of the custom board which is something between IDK_AM437x and EVM_AM437x. I also have the original IDK_AM437x board for the reference.

I can run the EtherCAT slave on the original IDK_AM437x board and it works flawlessly. The IDK_AM437x has TLK105 but my board has TLK106, I got both specs and I found no difference in pinout or registers, so I suppose there should be no SW changes related to TLK105/106.

On my custom HW among other changes I have these:

1) 3x pins are used in output to reset each PHY independently:

Pin T22, to reset the MII1 PHY

Pin T21, to reset the PRU0 PHY

Pin T20, to reset the PRU1 PHY

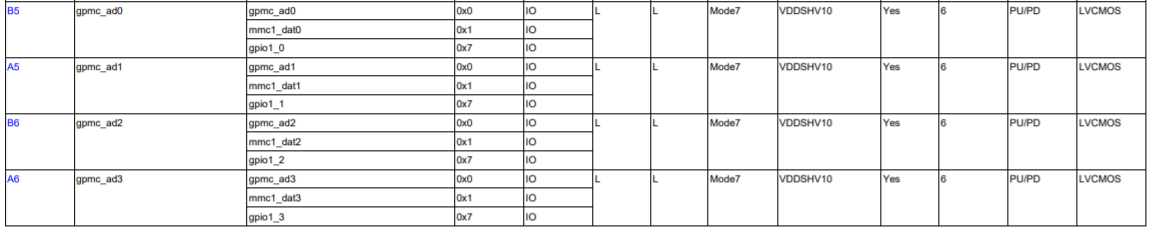

2) We add 4x debug leds. They are connected respectively on B5, A5, B6 and A6.

As I see from the schematics on the IDK board only Pin 20 is used for the reset

in the C:\ti\PRU-ICSS-EtherCAT_Slave_01.00.07.02\examples\board\idkAM437x\board_phy.c I see this code:

/*PRUETH0_RESETn */

PhyResetInfo[0].pin = 20;

PhyResetInfo[0].baseAddr = SOC_GPIO4_REG;

...

GPIOModuleEnable(PhyResetInfo[0].baseAddr);

GPIODirModeSet(PhyResetInfo[0].baseAddr, PhyResetInfo[0].pin, GPIO_DIR_OUTPUT);

GPIOPinWrite(PhyResetInfo[0].baseAddr, PhyResetInfo[0].pin, GPIO_PIN_LOW);

Board_delay(1000);

GPIOPinWrite(PhyResetInfo[0].baseAddr, PhyResetInfo[0].pin, GPIO_PIN_HIGH);

Board_delay(100000);

But as I need to set to TRUE all three pins, I try to modify the code this way:

/*PRUETH0_RESETn */

PhyResetInfo[0].pin = 20;

PhyResetInfo[0].baseAddr = SOC_GPIO4_REG;

/*PRUETH1_RESETn */

PhyResetInfo[1].pin = 21;

PhyResetInfo[1].baseAddr = SOC_GPIO4_REG;

/*MII1_RESETn */

PhyResetInfo[2].pin = 22;

PhyResetInfo[2].baseAddr = SOC_GPIO4_REG;

And then...

for (i = 0; i < (sizeof(PhyResetInfo)/sizeof(PhyResetInfo[0])); i++)

{

GPIOModuleEnable(PhyResetInfo[i].baseAddr);

GPIODirModeSet(PhyResetInfo[i].baseAddr, PhyResetInfo[i].pin, GPIO_DIR_OUTPUT);

GPIOPinWrite(PhyResetInfo[i].baseAddr, PhyResetInfo[i].pin, GPIO_PIN_LOW);

Board_delay(1000);

GPIOPinWrite(PhyResetInfo[i].baseAddr, PhyResetInfo[i].pin, GPIO_PIN_HIGH);

Board_delay(100000);

}

EtherCAT is NOT working on the custom board. I see that one port is activated (not the one I need for the ECAT) but others are not. When I connect cables to my laptop I don't see that ports are active.

I used the offline PinMux tool to describe the pins but I found no clear example how to use files "am43xx_pinmux.h" and "am43xx_pinmux_data.c" in my program.

How can I understand that pin T20 belongs to SOC_GPIO4_REG group? Where do belong A5, B5, A6, B6?

I see that function GPIOPinWrite() is used to control the GPIO:

void GPIOPinWrite(uint32_t baseAdd,

uint32_t pinNumber,

uint32_t pinValue);

But how do I know the base address?

How do I know to which base address belongs any my pin?

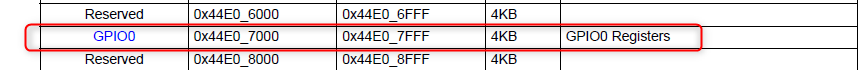

I see that in the EtherCAT slave example these base addresses are used:

#define SOC_GPIO0_REG (0x44e07000U)

#define SOC_GPIO1_REG (0x4804c000U)

#define SOC_GPIO2_REG (0x481ac000U)

#define SOC_GPIO3_REG (0x481ae000U)

#define SOC_GPIO4_REG (0x48320000U)

#define SOC_GPIO5_REG (0x48322000U)

Where do these numbers come from?

I will be very grateful for any help as I'm really stuck with this task. Seemed like a simple task, but lack of understanding of how to control GPIO blocks me from get things done.

Any help will be very appreciated!