Other Parts Discussed in Thread: TMS320DM8168

Tool/software: Linux

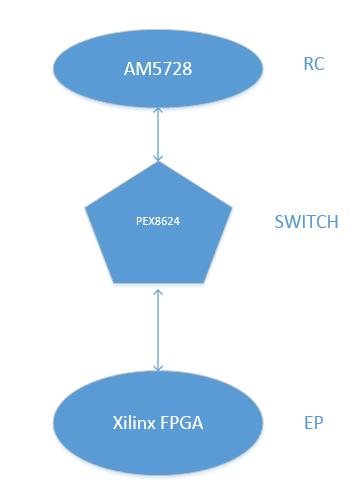

Hi ,our custom board based on AM5728 idk referenc.the topology of the pcie as follow figure

we load the ep program before the system on am5728 boot up, we enter the commond lspci in the consol, the return information just have the the device am5728 and the PXEX8624,there's no infromation about the fpga.the result show as follow picture,

if we replace the am5728 board by the TMS320DM8168 board,the device information can be get correctly.the sdk version is ti-processor-sdk-linux-rt-am57xx-evm-03.03.00.04,the dts about the pcie in the am572x-idk.dts file:

&pcie1_rc {

status = "okay";

};

&pcie1_ep {

};

just remove the "gpios = <&gpio3 23 GPIO_ACTIVE_HIGH>;" because we not used.

do we need some operate to config the kernel? or is there some method to solve this? we searched the issue on the forum,but have no similar link posted. thanks for someone to help us.