- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

I want to run AFE7950EVM on HTG-Z920.

I have reference design for ZC706, but the gtx_8b10b_rxtx ip is not supported.

Can TI provide reference for HTG-Z920(core : Xilinx ZYNQ UltraScale+ ZU19-L2 xczu19eg-ffvc1760-2-e )?

Hi Chaoyang,

The ZC706 FPGA supports the GTX transceiver which is not the same for the Zync US+, so it cannot be used as a starting point for the design. For Zync US+ the zcu102 and vcu118 reference designs should be used as a starting point. If the transceiver class is GTH you can use the zcu102 reference design as a starting point. If the transceiver class is GTY then the vcu118 reference design can be used a starting point.

Regards,

David Chaparro

Hi David,

I want to run the 4T4R2F reference design of ZC706 on HTG-Z920.

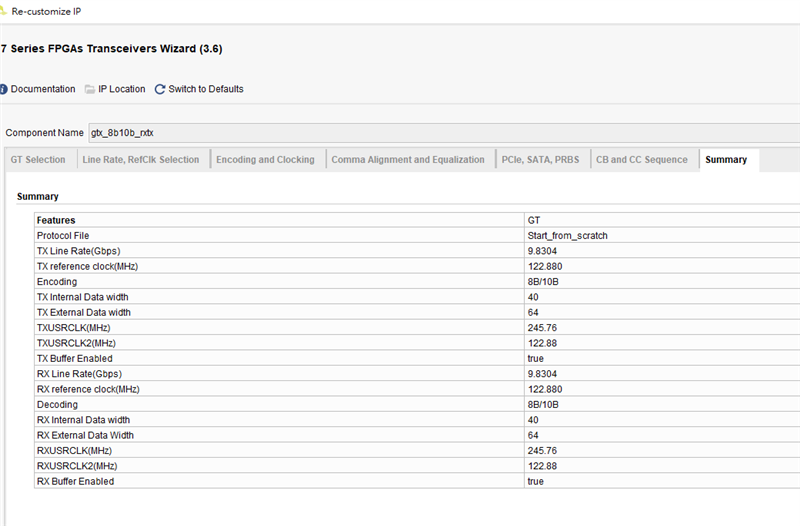

The ZC706 transceiver wizard summary is as following pic.

I want to modify the vcu118 reference design to meet my goal.

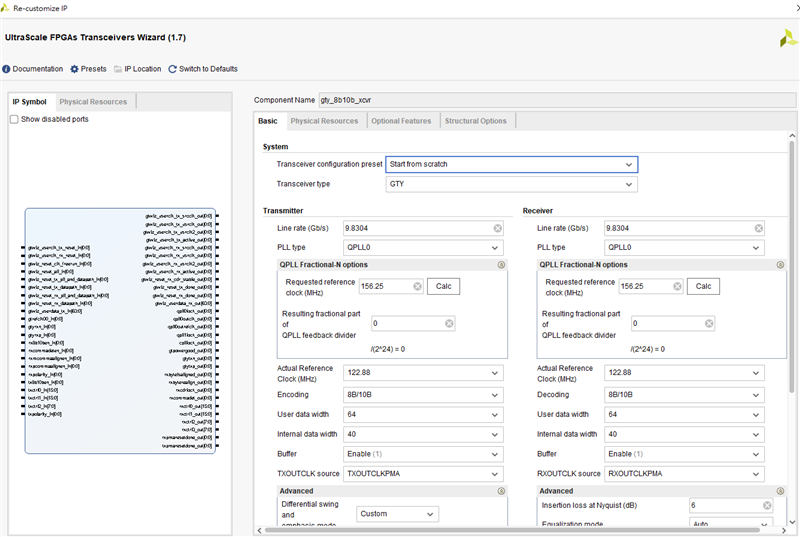

I modify the line rate to 9.8304, requested reference clock to 122.88, actual reference clock to 122.88, free-running and DRP clock frequency to 122.88.

When the transceiver wizard is reopend, the requested reference clock changeed back to 156.25.

Vivado shows error while compile.

What should I do?

Hi Chaoyang,

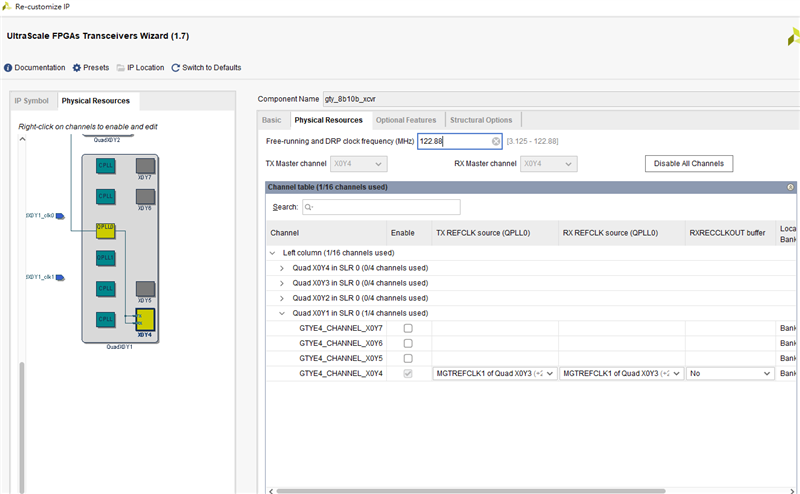

The requested reference clock input does not matter as long as the actual reference clock is set to 122.88MHz. In the transceiver IP you should also select the lanes in the quad that you will be using and also select which quad the GTX clock is going to (This can be seen by looking at the schematics).

Did you make any other changes to the reference design?

Regards,

David Chaparro

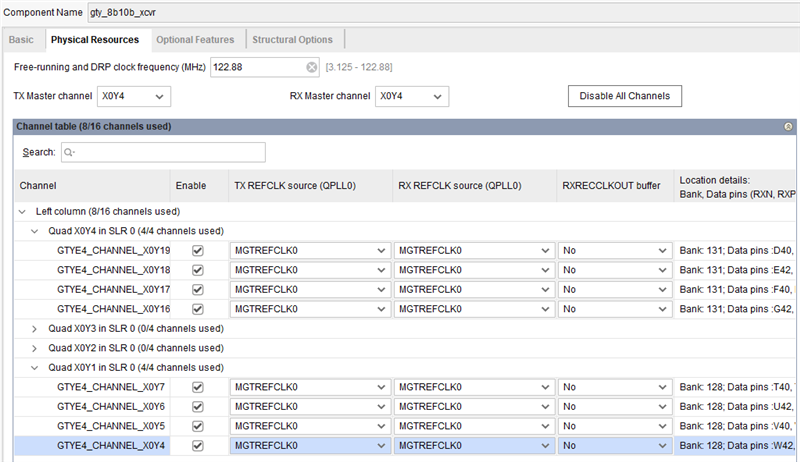

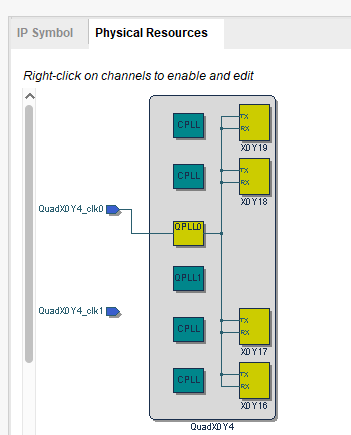

I enable the channels as below.

And I add pin locations in .xdc, update jesd_link_params.vh for 4T4R2FB mode and update sys_pll with 122..88MHz.

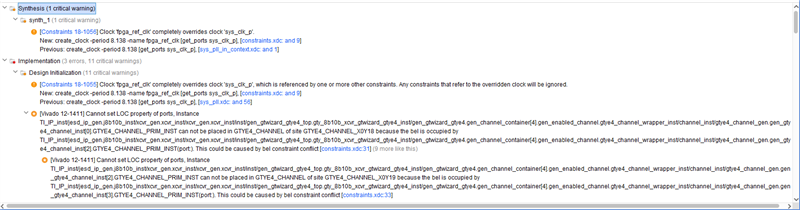

Vivado shows some errors.

[Vivado 12-1411] Cannot set LOC property of ports, Instance TI_IP_inst/jesd_ip_gen.j8b10b_inst/xcvr_gen.xcvr_inst/xcvr_gen.xcvr_inst/inst/gen_gtwizard_gtye4_top.gty_8b10b_xcvr_gtwizard_gtye4_inst/gen_gtwizard_gtye4.gen_channel_container[4].gen_enabled_channel.gtye4_channel_wrapper_inst/channel_inst/gtye4_channel_gen.gen_gtye4_channel_inst[2].GTYE4_CHANNEL_PRIM_INST can not be placed in GTYE4_CHANNEL of site GTYE4_CHANNEL_X0Y19 because the bel is occupied by TI_IP_inst/jesd_ip_gen.j8b10b_inst/xcvr_gen.xcvr_inst/xcvr_gen.xcvr_inst/inst/gen_gtwizard_gtye4_top.gty_8b10b_xcvr_gtwizard_gtye4_inst/gen_gtwizard_gtye4.gen_channel_container[4].gen_enabled_channel.gtye4_channel_wrapper_inst/channel_inst/gtye4_channel_gen.gen_gtye4_channel_inst[3].GTYE4_CHANNEL_PRIM_INST(port:). This could be caused by bel constraint conflict ["C:/X/vcu118_8b10b/source/constraints.xdc":33]

[Place 30-739] Sub-optimal placement for an IBUFDS_GT / GT component pair.If this sub optimal condition is acceptable for this design, you may use the CLOCK_DEDICATED_ROUTE constraint in the .xdc file to demote this message to a WARNING. However, the use of this override is highly discouraged. These examples can be used directly in the .xdc file to override this clock rule.

< set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets TI_IP_inst/jesd_ip_gen.j8b10b_inst/xcvr_gen.xcvr_inst/gt_refclk0_buf] >

TI_IP_inst/jesd_ip_gen.j8b10b_inst/xcvr_gen.xcvr_inst/genblk1[0].IBUFDS_GTE4_INST (IBUFDS_GTE4.O) is locked to GTYE4_COMMON_X0Y4

TI_IP_inst/jesd_ip_gen.j8b10b_inst/xcvr_gen.xcvr_inst/xcvr_gen.xcvr_inst/inst/gen_gtwizard_gtye4_top.gty_8b10b_xcvr_gtwizard_gtye4_inst/gen_gtwizard_gtye4.gen_common.gen_common_container[1].gen_enabled_common.gtye4_common_wrapper_inst/common_inst/gtye4_common_gen.GTYE4_COMMON_PRIM_INST (GTYE4_COMMON.GTREFCLK00) is provisionally placed by clockplacer on GTYE4_COMMON_X0Y1

The above error could possibly be related to other connected instances. Following is a list of

all the related clock rules and their respective instances.

The loc in xdc is checked. It is OK.

What else should I do?

I update the xdc and the vivado shows no error now.

I configure AFE7950 by the script of zc706 for 4T4R2F mode.

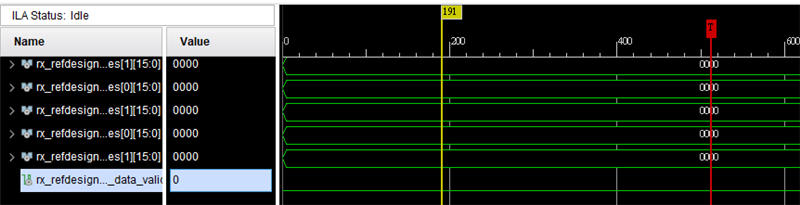

But, the rx valid is always low, qpll0_locked is 2, and cfg_rx_buffer_release_delay is 0.

Led D3 PLL2 LOCKED is on. LED 1/2/4 are off.

What might cause the problem?

What can I do to debug?

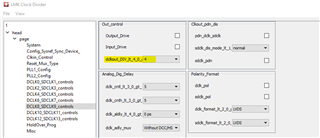

The transceiver needs 2 gtrefclks from dclk0/9 of LMK.

But the dclk9 is not enabled and the freq value is not as dclk0.

How to enable and set freq of the dclk 9 of LMK in Latte ?

Hi Chaoyang,

To change the LMK settings you can select 'LMK Clock Divider' from the Device List, on the right side of the Latte software. This will open another window where you can update the divider factor for the DCLK9, highlighted below.

To read back the LMK settings you must first change the LMK read out mode to 3 wire SPI. To do this you have to go to the View tab and select 'View RegProgrammer' then you can change the read out mode to 3 wire SPI. Now when you right click on a setting and press 'Get Value' you can read back the correct value.

Regards,

David Chaparro