Other Parts Discussed in Thread: AFE7950, , LMK04828

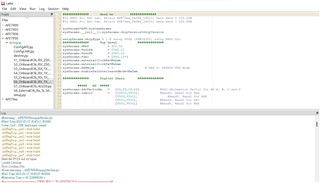

I made a ADC EVM ( AFE7950 ) similar to AFE7950EVM

The difference is below:

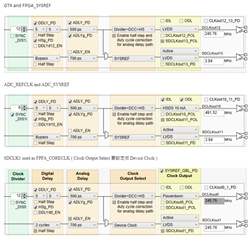

LMK04828 output channel in TI's AFE7950EVM v.s. ADC EVM I made

DCLK0 GTX v.s. DCLK12

SDCLK1 FPGA_SYSREF v.s. SDLCK13

DCLK2 ADC_REFCLK v.s. DCLK10

SDCLK3 ADC_SYSREF v.s. SDCLK11

SDCLK9 FPGA_REFCLK2 v.s. DCLK0

DCLK12 FPFA_CORECLK v.s. SDCLK1

p.s. The rest is the same including TX, RX, SYNC.....

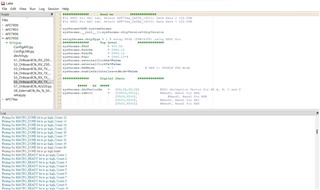

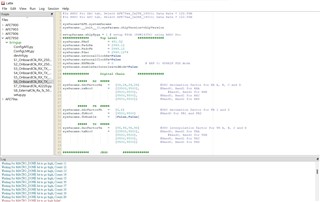

Here's my question: How can I modify the software latte so that the LMK04828 has the correct output

p.s. I tried to modify LMK output according to the E2E forum article

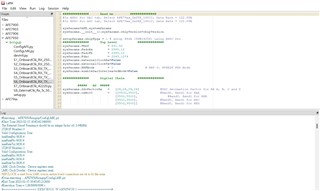

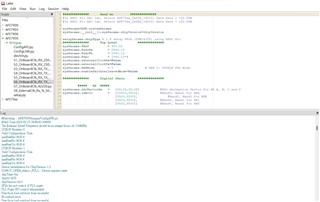

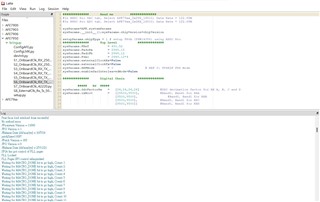

I found that it can only modify the LMK when I change the parameter in the LMK Clock Divider.

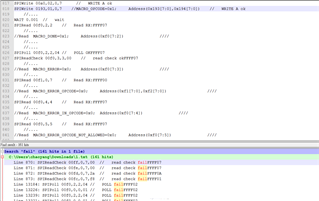

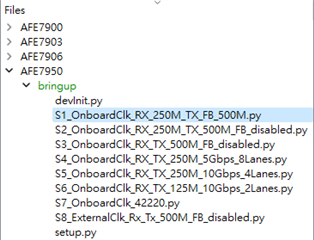

But once I run the script such as S1_OnboardCLK_RX_250M_TX_FB_500M.py

the LMK reset to previous setting so the ADC can't find the REFCLK !!

Pls help~ Thanks~