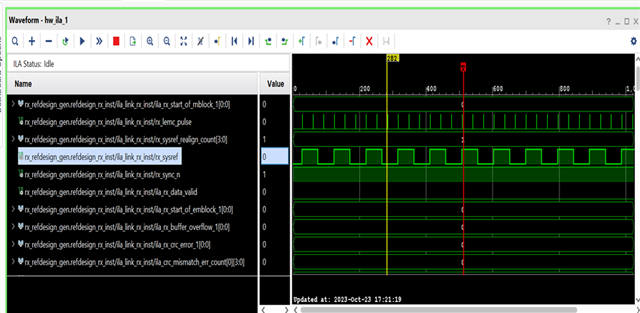

I have run into a problem porting the zcu102_64b66b reference design from a 8 lane design to a 2 lane design. The TI xzcu102 64/66 bit reference design with 8 JESD lanes, for evaluation of the AFE7950 on the EVM7950 works reliably with 8 lanes as supplied but does not work when reconfigured to work over 2 lanes with the porting changes. The TX side, ie DAC side is delivering tones however the RX side never demonstrates a data valid active in the FPGA to indicate that the FPGA transceiver is locking on to a valid JESD stream from the AFE7950. The following is a capture of the behavior on the RX side as captured using the Vivado HW debug tool integrated with the design. I have also included a document detailing the changes that I determined as necessary from the instruction supplied with the reference design. I would appreciate any help with uncovering why this is not working. Thanks