- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: TRF1208-AFE7950EVM

Tool/software:

Hi

I am taking the first steps to master the AFE7950 using the TSW14J57EVM using the AFE7950+TSW14J57.pptx method.

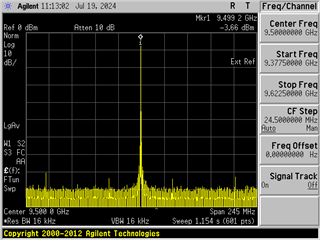

At step 5, instead of one harmonic at a frequency of (9500+9.9525) MHz, I see two harmonics at frequencies 9505 and 9509 MHz. What causes the harmonic at 9505 MHz?

There are no problems with powering the devices: directly on the AFE7950EVM board 5.1 V (current 3.7 A), directly on the TSW14J57EVM board 12.1 V (current 1.8 A).

I am attaching explanatory screenshots and logLatte.

Thanks in advance, Andrey

#======

#Executing .. AFE7950/bringup/setup.py

#Start Time 2024-06-18 11:35:38.878000

AFE79xxLibraryPG1p0

spi - USB Instrument created.

resetDevice

Kintex RegProgrammer - USB Instrument created.

Kintex RegProgrammer - USB Instrument created.

Kintex RegProgrammer - USB Instrument created.

#Done executing .. AFE7950/bringup/setup.py

#End Time 2024-06-18 11:35:48.111000

#Execution Time = 9.23300004005 s

#================ ERRORS:0, WARNINGS:0 ================#

#======

#Executing .. AFE7950/bringup/devInit.py

#Start Time 2024-06-18 11:39:22.260000

Power Card - USB Instrument created.

Reset the FPGA and try again.

Loaded Libraries

Refreshed GUI

#Done executing .. AFE7950/bringup/devInit.py

#End Time 2024-06-18 11:40:48.178000

#Execution Time = 85.9179999828 s

#================ ERRORS:1, WARNINGS:0 ================#

#======

#Executing .. AFE7950/bringup/S1_OnboardClk_RX_250M_TX_FB_500M.py

#Start Time 2024-06-18 11:45:28.578000

The External Sysref Frequency should be an integer factor of: 3.84MHz

2T2R1F Number: 0

Valid Configuration: True

laneRateRx: 9830.4

laneRateFb: 9830.4

laneRateTx: 9830.4

2T2R1F Number: 1

Valid Configuration: True

laneRateRx: 9830.4

laneRateFb: 9830.4

laneRateTx: 9830.4

LMK Clock Divider - Device registers reset.

LMK Clock Divider - Device registers reset.

REFCLOCK is used from LMK source, ensure board connections are ok to do the same

LMK and FPGA Configured.

DONOT_OPEN_Atharv_FULL - Device registers reset.

chipType: 0xa

chipId: 0x78

chipVersion: 0x11

AFE Reset Done

Fuse farm load autoload done successful

No autload error

Fuse farm load autoload done successful

No autload error

AFE MCU Wake up done and patch loaded.

PLL Locked

AFE PLL Configured.

AFE SerDes Configured.

AFE Digital Chains configured.

AFE TX Analog configured.

AFE RX Analog configured.

AFE FB Analog configured.

AFE JESD configured.

AFE AGC configured.

AFE GPIO configured.

Sysref Read as expected

###########Device DAC JESD-RX 0 Link Status###########

Serdes-FIFO error for lane 0: 1

Serdes-FIFO error for lane 1: 1

Serdes-FIFO error for lane 2: 1

Serdes-FIFO error for lane 3: 1

Comma Align Lock Lane0: False; Please check if the transmitter is sending data and eye is good.

Comma Align Lock Lane1: False; Please check if the transmitter is sending data and eye is good.

Comma Align Lock Lane2: False; Please check if the transmitter is sending data and eye is good.

Comma Align Lock Lane3: False; Please check if the transmitter is sending data and eye is good.

CS State TX0: 0b00000000 . It is expected to be 0b10101010

FS State TX0: 0b00000000 . It is expected to be 0b01010101

Couldn't get the link up for device RX: 0; Alarms: 0xf000

###################################

###########Device DAC JESD-RX 1 Link Status###########

Serdes-FIFO error for lane 0: 1

Serdes-FIFO error for lane 1: 1

Serdes-FIFO error for lane 2: 1

Serdes-FIFO error for lane 3: 1

Comma Align Lock Lane0: False; Please check if the transmitter is sending data and eye is good.

Comma Align Lock Lane1: False; Please check if the transmitter is sending data and eye is good.

Comma Align Lock Lane2: False; Please check if the transmitter is sending data and eye is good.

Comma Align Lock Lane3: False; Please check if the transmitter is sending data and eye is good.

CS State TX0: 0b00000000 . It is expected to be 0b10101010

FS State TX0: 0b00000000 . It is expected to be 0b01010101

Couldn't get the link up for device RX: 1; Alarms: 0xf000

###################################

AFE Configuration Complete

#Done executing .. AFE7950/bringup/S1_OnboardClk_RX_250M_TX_FB_500M.py

#End Time 2024-06-18 11:46:08.822000

#Execution Time = 40.243999958 s

#================ ERRORS:18, WARNINGS:1 ================#

###########Device DAC JESD-RX 0 Link Status###########

CS State TX0: 0b10101010 . It is expected to be 0b10101010

FS State TX0: 0b01010101 . It is expected to be 0b01010101

Could get the link up for device RX: 0

###################################

###########Device DAC JESD-RX 1 Link Status###########

CS State TX0: 0b10101010 . It is expected to be 0b10101010

FS State TX0: 0b01010101 . It is expected to be 0b01010101

Could get the link up for device RX: 1

###################################

#======

###########Device DAC JESD-RX 0 Link Status###########

CS State TX0: 0b10101010 . It is expected to be 0b10101010

FS State TX0: 0b01010101 . It is expected to be 0b01010101

Could get the link up for device RX: 0

###################################

###########Device DAC JESD-RX 1 Link Status###########

CS State TX0: 0b10101010 . It is expected to be 0b10101010

FS State TX0: 0b01010101 . It is expected to be 0b01010101

Could get the link up for device RX: 1

###################################

#======

###########Device DAC JESD-RX 0 Link Status###########

CS State TX0: 0b10101010 . It is expected to be 0b10101010

FS State TX0: 0b01010101 . It is expected to be 0b01010101

Could get the link up for device RX: 0

###################################

###########Device DAC JESD-RX 1 Link Status###########

CS State TX0: 0b10101010 . It is expected to be 0b10101010

FS State TX0: 0b01010101 . It is expected to be 0b01010101

Could get the link up for device RX: 1

###################################

#======

###########Device DAC JESD-RX 0 Link Status###########

CS State TX0: 0b10101010 . It is expected to be 0b10101010

FS State TX0: 0b01010101 . It is expected to be 0b01010101

Could get the link up for device RX: 0

###################################

###########Device DAC JESD-RX 1 Link Status###########

CS State TX0: 0b10101010 . It is expected to be 0b10101010

FS State TX0: 0b01010101 . It is expected to be 0b01010101

Could get the link up for device RX: 1

###################################

#======

###########Device DAC JESD-RX 0 Link Status###########

CS State TX0: 0b10101010 . It is expected to be 0b10101010

FS State TX0: 0b01010101 . It is expected to be 0b01010101

Could get the link up for device RX: 0

###################################

###########Device DAC JESD-RX 1 Link Status###########

CS State TX0: 0b10101010 . It is expected to be 0b10101010

FS State TX0: 0b01010101 . It is expected to be 0b01010101

Could get the link up for device RX: 1

###################################

#======

Hi Andrey,

I suspect that this issue would be caused by an incorrect setting on the HSDC Pro side, such as an issue with the ini file. Can you confirm that you are following the AFE79xx bringup guide for the TSW14J57 that is available in the AFE79xx secure folder? If not I would recommend to try the mode outlined and see if that fixes the spur issue. The bringup guide will have the settings for HSDC Pro and outline the required bringup procedure.

Regards,

David Chaparro

Hi David,

I indicated that I used the instructions AFE7950+TSW14J57.pptx, which was obtained from the AFE79xx_Bringup_Guides.zip archive. There is a very simple procedure for configuring FPGA, AFE and LMC on pages 6 and 7.

If you have some other instructions in mind, then please indicate the exact name of the required file, which is located in a protected folder. I didn't find anything else like it there.

Regards,

Andrey

Hi Andrey,

If the ppt was taken from the AFE79xx_Bringup_Guides.zip archive then that is the correct one. My suspect would then be on the ini file in HSDC Pro. Is this issue seen across all Tx channels.

Can you take a look at the ini file settings and confirm that they match the attached file? (Ini file can be found at the following location: C:\Program Files\Texas Instruments\High Speed Data Converter Pro\14J57revE Details\DAC files)

One additional test to verify if it is related to the tone send by the FPGA is to configure the DAC into a NCO test pattern mode using the writes given below.

enable=1 for i in range(4): CAFE.dacJesdConstantTestPatternEnable(0,i,enable) CAFE.dacJesdConstantTestPatternValue(0,i,0,0,35536) #0, chNo, bandNo, valueI, valueQ

Regards,

David Chaparro

Thank you, David.

The day after tomorrow I will check the contents of the specified ini file on my work computer.

Regarding the code:

enable=1

for i in range(4):

CAFE.dacJesdConstantTestPatternEnable(0,i,enable)

CAFE.dacJesdConstantTestPatternValue(0,i,0,0,35536) #0, chNo, bandNo, valueI, valueQ

Where should it be entered, in the Latte command line?

And what should be the result?

Regards,

Andrey

Hi Andrey,

I would suggest creating a seperate script for the code and run the script when testing the DAC in the NCO only mode. When you run those lines the DAC will be configured to output the NCO frequency directly, ignoring the data from the FPGA. So you should see a CW tone at the NCO frequency.

Regards,

David Chaparro

Hello David.

The INI files are identical.

After the usual procedure, running the file S1_OnboardClk_RX_250M_TX_FB_500MT.py, I again got two harmonics instead of one. Then I ran your 4-line code in Latte as a py-file. But apparently I didn’t make this file correctly, because Latte threw an error and nothing in the spectrum changed. Here is Latte's log.

#================ ERRORS:1, WARNINGS:0 ================# #====== #Executing .. AFE7950/bringup/S1_OnboardClk_RX_250M_TX_FB_500M.py #Start Time 2024-06-23 12:00:59.503000 The External Sysref Frequency should be an integer factor of: 3.84MHz 2T2R1F Number: 0 Valid Configuration: True laneRateRx: 9830.4 laneRateFb: 9830.4 laneRateTx: 9830.4 2T2R1F Number: 1 Valid Configuration: True laneRateRx: 9830.4 laneRateFb: 9830.4 laneRateTx: 9830.4 LMK Clock Divider - Device registers reset. LMK Clock Divider - Device registers reset. REFCLOCK is used from LMK source, ensure board connections are ok to do the same LMK and FPGA Configured. DONOT_OPEN_Atharv_FULL - Device registers reset. chipType: 0xa chipId: 0x78 chipVersion: 0x11 AFE Reset Done Fuse farm load autoload done successful No autload error Fuse farm load autoload done successful No autload error AFE MCU Wake up done and patch loaded. PLL Locked AFE PLL Configured. AFE SerDes Configured. AFE Digital Chains configured. AFE TX Analog configured. AFE RX Analog configured. AFE FB Analog configured. AFE JESD configured. AFE AGC configured. AFE GPIO configured. Sysref Read as expected ###########Device DAC JESD-RX 0 Link Status########### CS State TX0: 0b10101010 . It is expected to be 0b10101010 FS State TX0: 0b01010101 . It is expected to be 0b01010101 Could get the link up for device RX: 0 ################################### ###########Device DAC JESD-RX 1 Link Status########### CS State TX0: 0b10101010 . It is expected to be 0b10101010 FS State TX0: 0b01010101 . It is expected to be 0b01010101 Could get the link up for device RX: 1 ################################### AFE Configuration Complete #Done executing .. AFE7950/bringup/S1_OnboardClk_RX_250M_TX_FB_500M.py #End Time 2024-06-23 12:01:41.530000 #Execution Time = 42.0269999504 s #================ ERRORS:0, WARNINGS:1 ================# #====== #Executing .. AFE7950/bringup/DAC in the NCO only mode.py #Start Time 2024-06-23 12:02:14.404000 #Error: afeCTestWrapper instance has no attribute 'dacJesdConstantTestPatternEnable' # "AFE7950/bringup/DAC in the NCO only mode.py", line 3, in # AttributeError: afeCTestWrapper instance has no attribute 'dacJesdConstantTestPatternEnable' # # #Done executing .. AFE7950/bringup/DAC in the NCO only mode.py #End Time 2024-06-23 12:02:14.413000 #Execution Time = 0.0090000629425 s #================ ERRORS:1, WARNINGS:0 ================#

Regards,

Andrey

Hi Andrey,

Please try the updated lines below for NCO only mode.

for i in [0,1]: for j in [0,1]: AFE.JESD.DACJESD[i].dacJesdConstantTestPatternValue(1,j,0,35536,0) # enable, channelNum, bandNum, Ival, Qval

On the TSW14J57 can you report the status of the LEDs?

Regards,

David Chaparro

Hi David,

I tried running the updated lines for NCO only mode.

I am attaching screenshots of “before”, “after” and windows with this code. As you can see, the result does not meet expectations. In addition, the spectrum became dirtier than it previously was during my previous treatment.

The voltages directly on the boards are 12.2 V (current 1.8 A) and 5.1 V (current 3.7 A).

LED status on TSW14J57:

D1 - lights up or not (can change each time you press the SEND button);

D2 - started blinking only after the combination was launched (S1_OnboardClk_RX_250M_TX_FB_500M, AFE.adcDacSync(), SEND, SEND). It didn’t shine before;

D3 - always shines;

D4 - does not shine;

D5 - initially it shone brightly, but after launching S1_OnboardClk_RX_250M_TX_FB_500M it began to shine dimly;

D6 - shines;

D7 - does not shine;

D8 and D9 - always shine;

D10,11,13,14,15,17,18,19 (blue) - shine;

D16,22 - do not shine.

Sincerely,

Andrey

Hi Andrew,

The spectrum that you are seeing is not expected. Is this same issue seen on all channels or is it isolated to a single channel?

If you lower the amplitude of the output tone do you see any changes in the spectrum? To do this in the NCO only mode you can change the ‘35536’ to ‘8192’ in the function provided previously.

Regards,

David Chaparro

Hello David!

All channels behave the same.

However, the harmonic amplitudes in the ТхВ and ТхД channels are lower than the amplitudes in the ТхА and ТхС channels by approximately 20 dB at the same noise level.

In the "NCD only" mode, the spectra are simply shifted to the left by 9.5 MHz.

When moving from a value of 35336 to a value of 8192, the harmonic amplitudes in all channels decrease by approximately 10 dB while maintaining the same noise level.

David, the problem is not being solved. If you have no idea how to fix it, maybe your company will provide us with another, working kit?

Best wishes, Andrey

The pictures are arranged in the following order:

TxA,B,C,D after the standard script S1_OnboardClk_RX_250M_TX_FB_500M.py.

Then TxA,B in the “NCO only” mode with parameter 35336.

Then TxA,B in the “NCO only” mode with parameter 8192.

Hi Andrey,

Based on the fact that the issue is seen in NCO only configuration then the issue is either with the AFE configuration or the EVM hardware. One suggestion would be to try a different configuration on the AFE. Can you test the S3 configuration script?

Additionally, has the script S1 been modified in any way?

Regards,

David Chaparro

Hi David.

No, I did not change the S1 script, which should be clear from the Latte log that I posted here on June 23rd.

To begin with, I would like everything to work correctly with S1, as it is written in your instructions AFE7950+TSW14J57.pptx. I thought that I could master this platform using ready-made examples, and then quickly implement the functions I needed based on them, since I do not yet have time to independently understand the command system and register model of the AFE7950.

But I can try S3 too. At the same time, I need a priori information, what should I expect on the spectrum analyzer, following the example of the above instructions?

And even better, if you have instructions for detailed equipment diagnostics, I can immediately quickly collect all the information for your analysis, so as not to delay the solution to the problem.

Best wishes, Andrey

Hi David.

I looked at the S3 script. As I see, in terms of the transmitter it is no different from S1.

The results are also similar. I am attaching screenshots of TxA,B,C,D and logs.

With all respect, Andrey

#====== #Executing .. AFE7950/bringup/setup.py #Start Time 2024-07-14 12:00:07.093000 AFE79xxLibraryPG1p0 spi - USB Instrument created. resetDevice Kintex RegProgrammer - USB Instrument created. Kintex RegProgrammer - USB Instrument created. Kintex RegProgrammer - USB Instrument created. #Done executing .. AFE7950/bringup/setup.py #End Time 2024-07-14 12:00:14.865000 #Execution Time = 7.77200007439 s #================ ERRORS:0, WARNINGS:0 ================# #====== #Executing .. AFE7950/bringup/devInit.py #Start Time 2024-07-14 12:00:27.686000 Power Card - USB Instrument created. Reset the FPGA and try again. Loaded Libraries Refreshed GUI #Done executing .. AFE7950/bringup/devInit.py #End Time 2024-07-14 12:01:52.234000 #Execution Time = 84.5479998589 s #================ ERRORS:1, WARNINGS:0 ================# #====== #Executing .. AFE7950/bringup/S3_OnboardClk_RX_TX_500M_FB_disabled.py #Start Time 2024-07-14 12:05:31.841000 The External Sysref Frequency should be an integer factor of: 5.12MHz 2T2R1F Number: 0 Valid Configuration: True laneRateRx: 9830.4 laneRateFb: 9830.4 laneRateTx: 9830.4 2T2R1F Number: 1 Valid Configuration: True laneRateRx: 9830.4 laneRateFb: 9830.4 laneRateTx: 9830.4 LMK Clock Divider - Device registers reset. LMK Clock Divider - Device registers reset. REFCLOCK is used from LMK source, ensure board connections are ok to do the same LMK and FPGA Configured. DONOT_OPEN_Atharv_FULL - Device registers reset. chipType: 0xa chipId: 0x78 chipVersion: 0x11 AFE Reset Done Fuse farm load autoload done successful No autload error Fuse farm load autoload done successful No autload error AFE MCU Wake up done and patch loaded. PLL Locked AFE PLL Configured. AFE SerDes Configured. AFE Digital Chains configured. AFE TX Analog configured. AFE RX Analog configured. AFE FB Analog configured. AFE JESD configured. AFE AGC configured. AFE GPIO configured. Sysref Read as expected ###########Device DAC JESD-RX 0 Link Status########### Serdes-FIFO error for lane 0: 1 Serdes-FIFO error for lane 1: 1 Serdes-FIFO error for lane 2: 1 Serdes-FIFO error for lane 3: 1 Comma Align Lock Lane0: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane1: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane2: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane3: False; Please check if the transmitter is sending data and eye is good. CS State TX0: 0b00000000 . It is expected to be 0b10101010 FS State TX0: 0b00000000 . It is expected to be 0b01010101 Couldn't get the link up for device RX: 0; Alarms: 0xf000 ################################### ###########Device DAC JESD-RX 1 Link Status########### Serdes-FIFO error for lane 0: 1 Serdes-FIFO error for lane 1: 1 Serdes-FIFO error for lane 2: 1 Serdes-FIFO error for lane 3: 1 Comma Align Lock Lane0: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane1: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane2: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane3: False; Please check if the transmitter is sending data and eye is good. CS State TX0: 0b00000000 . It is expected to be 0b10101010 FS State TX0: 0b00000000 . It is expected to be 0b01010101 Couldn't get the link up for device RX: 1; Alarms: 0xf000 ################################### AFE Configuration Complete #Done executing .. AFE7950/bringup/S3_OnboardClk_RX_TX_500M_FB_disabled.py #End Time 2024-07-14 12:06:11.183000 #Execution Time = 39.3420000076 s #================ ERRORS:18, WARNINGS:1 ================# ###########Device DAC JESD-RX 0 Link Status########### Serdes-FIFO error for lane 0: 1 Serdes-FIFO error for lane 1: 1 Serdes-FIFO error for lane 2: 1 Serdes-FIFO error for lane 3: 1 Comma Align Lock Lane0: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane1: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane2: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane3: False; Please check if the transmitter is sending data and eye is good. CS State TX0: 0b00000000 . It is expected to be 0b10101010 FS State TX0: 0b00000000 . It is expected to be 0b01010101 Couldn't get the link up for device RX: 0; Alarms: 0xf000 ################################### ###########Device DAC JESD-RX 1 Link Status########### Serdes-FIFO error for lane 0: 1 Serdes-FIFO error for lane 1: 1 Serdes-FIFO error for lane 2: 1 Serdes-FIFO error for lane 3: 1 Comma Align Lock Lane0: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane1: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane2: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane3: False; Please check if the transmitter is sending data and eye is good. CS State TX0: 0b00000000 . It is expected to be 0b10101010 FS State TX0: 0b00000000 . It is expected to be 0b01010101 Couldn't get the link up for device RX: 1; Alarms: 0xf000 ################################### #====== ###########Device DAC JESD-RX 0 Link Status########### CS State TX0: 0b10101010 . It is expected to be 0b10101010 FS State TX0: 0b01010101 . It is expected to be 0b01010101 Could get the link up for device RX: 0 ################################### ###########Device DAC JESD-RX 1 Link Status########### CS State TX0: 0b10101010 . It is expected to be 0b10101010 FS State TX0: 0b01010101 . It is expected to be 0b01010101 Could get the link up for device RX: 1 ################################### #======