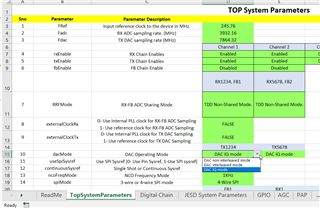

Other Parts Discussed in Thread: AFE8030, LMK04828

Tool/software:

Hi Team,

We have Multiple TI AFE8030EVM Setups. But from that only one Setup is working Without Frequency Offset. all other 5 setups are having Frequency Offset of ~30Mhz frequency Offset.

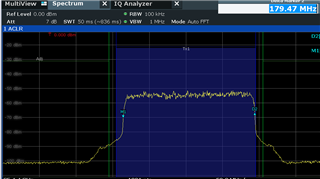

Working Setup

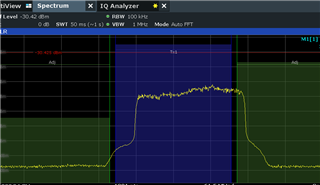

Frequency Offset Setup

everything in both the setups are same. executable we are running with same configs and .hex files.

How to Debug this issue ?

PFA config file.

3326.final_config_tx_a_b_rx_a_b.xlsx

Regards

P Shiva