Other Parts Discussed in Thread: LMK04828

Tool/software:

HI william pfennigwerth,

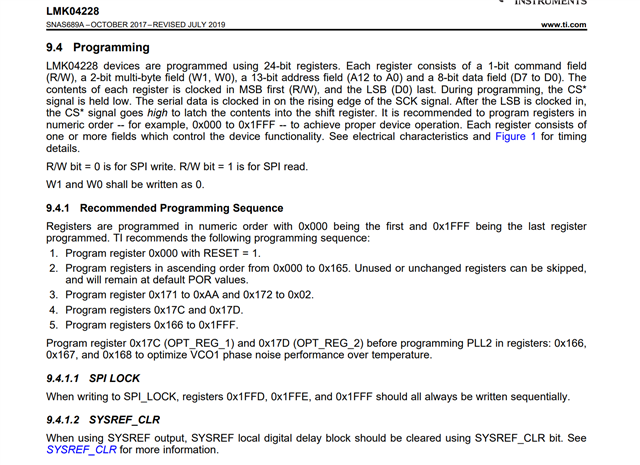

i am vamsi dealing with the offset issue in place of shiva, in the latest message you have mentioned about to check the PLL lock on the board,yes we have seen PLL is not locking(Status_LD2 is not high).in that you have mentioned that by disabling the R336 bit .for this problems can you help me with these

1)can you tell me at which point need to check the voltage of VCXO

2) how to change the R336 bit