Other Parts Discussed in Thread: LMK04832

Tool/software:

Hi,

We planned to use AFE7950 Part in our design.

In data sheet , SYSREF Requirements given as below.

Three SYSREF pulses are required to

completely synchronize the device.28. These three pulses are necessary to synchronize the N-divider (if

needed), clock divider for the digital logics, and the JESD204 link-up. SYSREF usage in the bring-up software

flow is described in the AFE79xx Configuration Guide available from TI. For each pulse, a SPI register latch is

programmed high, after which the 1st SYSREF pulse is captured and the following pulses are ignored. SYSREF

then would need to be held low for the SPI latch to be programmed low then high again for the next pulse. After

the 3 pulses, TI recommends that SYSREF is turned off or held low to prevent spurs coupling into the device

clock

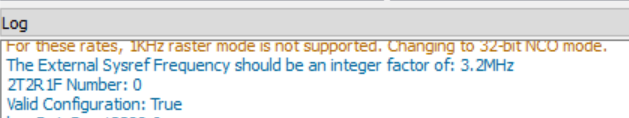

How to calculate the SYS-REF Clock frequency range ? In data sheet mentioned to refer the "Excel spreadsheet to calculate possible SYSREF frequencies is available from TI". Please share teh spreadsheet for reference.

And also what is the relationship between SPI latch to SYS-REF signal ? Why SYS-REF signal is referred with SPI signal?

Please share the detailed functional requirement of SYS-REF signal?