Hello, I am Minrak and working on TDC1000-7200 EVM module.

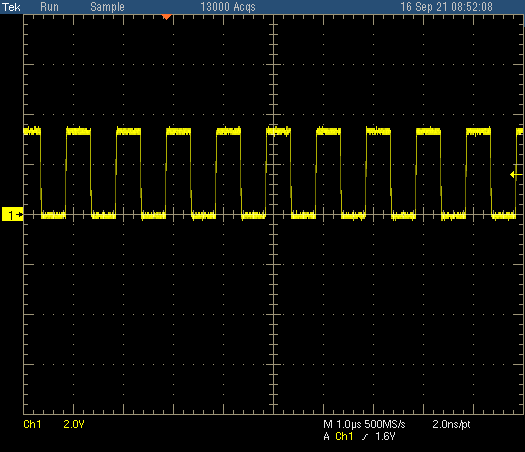

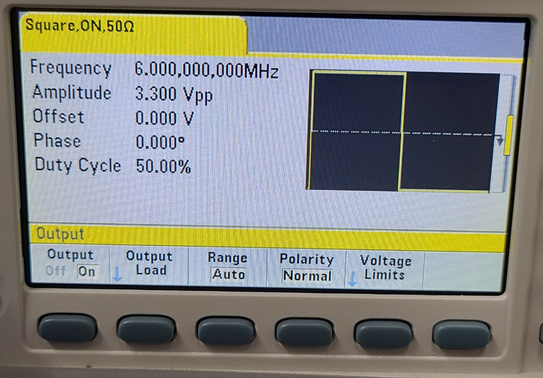

I have asked serial questions regarding the CPU or external clock in the previous post (https://e2e.ti.com/support/sensors-group/sensors/f/sensors-forum/1032912/tdc1000-regarding-external-clock-for-tdc1000-7200evm).

Still, I need help and please check the details of my situation in the previous post.

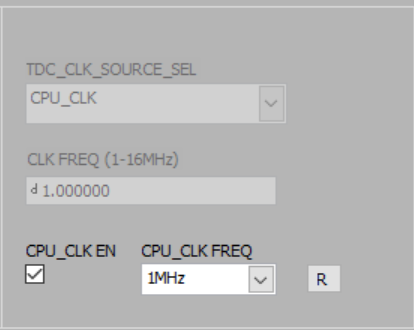

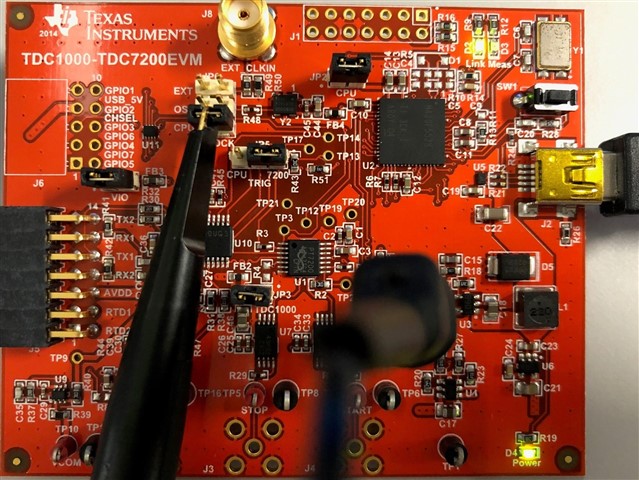

Regarding the last answer by "Jacob Nogaj", he mentioned "the module will not use the CPU clock for the TDC1000 unless JP6 is set to CPU. Given your settings, the only way to receive "NaN" in CH1_Field is to select a CPU clock in the GUI, but set JP6 to "EXT".

However, I did select CPU clock in GUI and set JP6 to "CPU". Whenever I set "JP6" to "CPU" or "EXT" to match GUI settings, it just stucks. GUI doesn't move and I need to shut down the program by force.

I followed everything correct as you see in the previous posts.

Please help me so that I can use CPU or EXT clocks for transducers I am using.

Best regards,

Minrak Kim