Could you point me towards documentation regarding the elapsed time in the radar after triggering a capture.

For example,

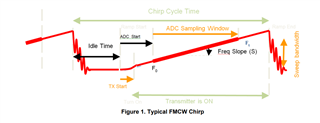

- once a trigger is received (whether from internal clock or hardware trigger) is there an approximation for how much time passes until the start of the capture period.

- the "exposure" itself I believe is described by the chirp, total exposure being PRI*NUM_CHIRPS

- expected duration for processing (not as important)

Essentially, we're curious how well we can approximate the "mid-point" of the exposure time, given knowledge of the trigger time. Is this feasible? As such the most interesting information for us is what happens between triggering and starting capturing.