Other Parts Discussed in Thread: IWR6843AOP, IWRL6432,

I have a couple of questions regarding hardware triggering. Note, SDK 3.5 Rev F.

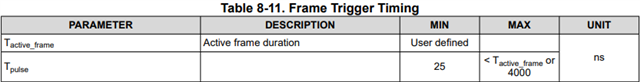

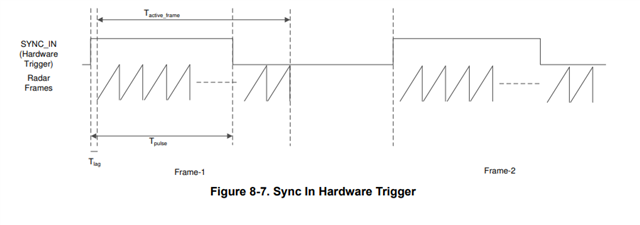

Following the below documentation I've assured the trigger is high for >25 ns and <1us. On the scope it goes from 215ns to 414ns.

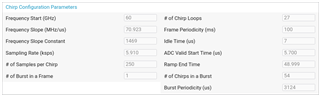

Does it really need to be less than 1us? I've ran the sensor with trigger signals > and < 1us and can't see a difference. This is of interest because 1us is a relatively strict requirement to fulfill and I can't see why it should need to be so small for a 10Hz measurement.