Other Parts Discussed in Thread: CC3220SF, IWR6843, AWR2243, , MMWAVEICBOOST, AWR1642BOOST

Hello Community,

On the custom board, we have IWR6843 connected with CC3220SF for our application.

We want to use just a single FLASH of CC3220SF for both images and on bootup of the board, I want to transfer the radar image into IWR6843 RAM.

My queries to TI:

1. Is there any example implementation by TI that I could use for this application? This will be helpful and will save a lot of time.

2. If I need to implement protocol by myself, which example should I refer to? How should begin with communication in this case?

3. Which chip will be the SPI Master here? Since communication is initiated by Radar, I think IWR6843 would be the master here.

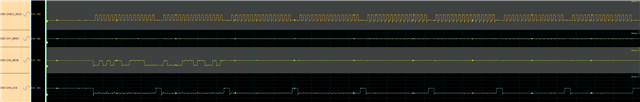

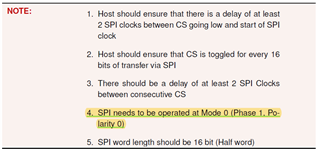

I have referred to the Bootloader flow swra6 for the SPI Bootmode and mmWave-Radar Interface Control document for SPI protocol.

Please let me know more information on this.

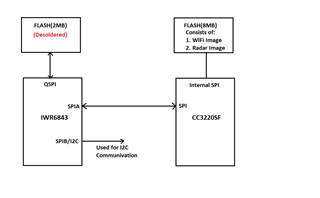

Below is the block diagram of the system we want to implement.

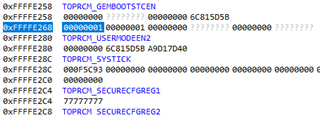

SPIA of IWR6843 MCU is connected with SPI of CC3220SF MCU. SPIB of IWR6843 is pin muxed to be used for I2C communication.

From one of our custom boards, we have removed the FLASH used by Radar MCU that used QSPI for communication.

Now since FLASH is absent ROM Bootloader will begin SPI bootmode using SPIA for communication to get image.

I need a communication protocol example to implement after this, to transfer the Radar Image from the FLASH of the WiFi chip to the RAM of IWR6843 MCU.

Thanks and Regards,

Swapnil