n AWR2243 cascaded system, slave devices use external frame syn signal for frame trigger and this frame sync signal will route back to host. There is frame trigger delay after sync in pulse input to real frame start (chirp transmit). What is the range of frame trigger delay time across different AWR2243 devices? Customer asked this question is that they plan to change phase shifter in each TX/chirp. They concerned that if there is a big difference on the frame trigger delay in different devices it will affect the ADC data and the detection result. Would you pls help? As the phase shifter accuracy on AWR2243 is ±5C, may the small different delay time not affect the result much?

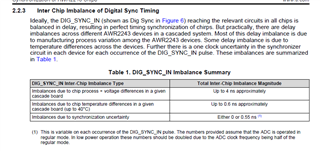

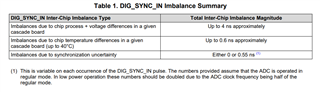

They should target to achieve less that 10ns imbalance. This is considering ~5ns imbalance due to process corner, voltage, temperature and pulse timing. So the PCB should be length matched to acheive ~5ns of delay or less.

the above information is the printed on the forum

our question is why the time imbalance should not extend 10ns, if extend 10ns, what problem or issue it should cause?