Hello,

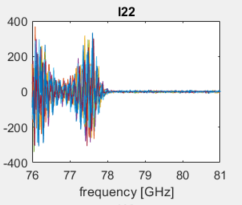

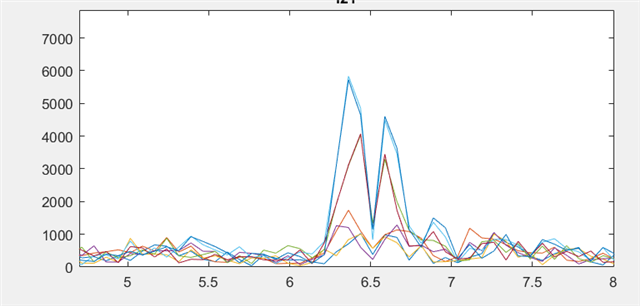

I am experiencing a similar issue to the one in the referenced post (AWR2243: Samples decay - Sensors forum - Sensors - TI E2E support forums) where the samples decay at the end of the chirp. I am using a master/slave configuration and this happens only in the slave device.

We noticed that changing the sample rate and the chirp slope to modify the bandwidth changes the result. In particular for lower bandwidth the number of zero samples decreases.

Do you have any insights on the reason it happens and how the choice of the parameters influences this behavior?

Thank you,

Camilla