Other Parts Discussed in Thread: AWR1843AOP, DCA1000EVM

Tool/software:

Hi TI,

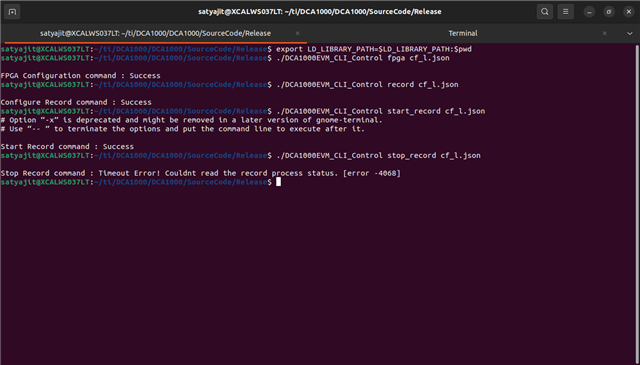

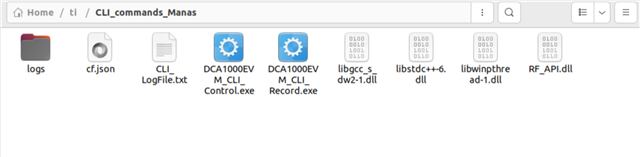

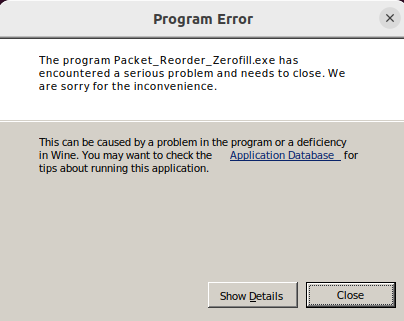

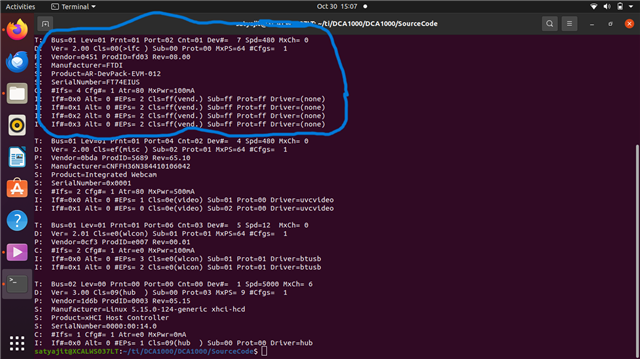

We are working on DCA1000 and AWR1843AOP EVM for raw data collection. For our application,we have to work on ubuntu system, So we decided to use DCA1000 CLI commands for raw data collection. In the DCA1000 CLI software user guide it is mentioned under system requirements for Linux systems as Ubuntu 16xx LTS 64-bit OS. In the ubuntu 20.04 version we connected the DCA1000 board and it is getting detected, but the drivers are coming as none. Please find the attached picture, in that under AR DEV pack ports are coming as none. Can you provide solution for this FTDI drivers?

Is it necessary to use ubuntu 16xx ? Can we use ubuntu 20.04 version?

Thank you,

With regards,

Rashmika