Tool/software:

Hello Experts,

i was building pcb design and wanted to know the bare-minimum requirements for PCB.

I don't even need traces like LVDS i only need UART connection ( of course pcb will be as per swr166 / sprr418 - required parts only )

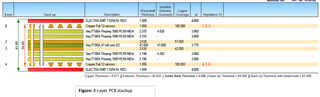

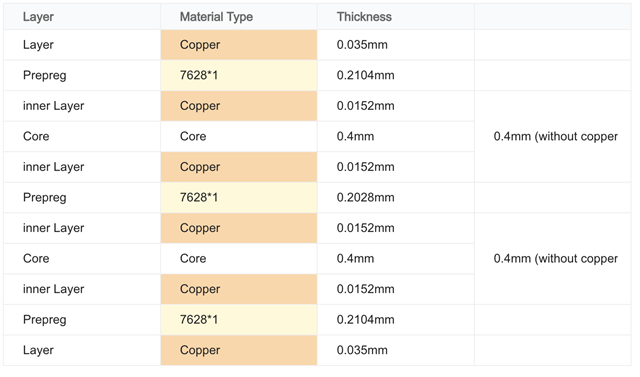

i have read pcb stacks that were available on xWR6843AOP_HW_BringUp_Schematic_and_Layout_Checklist.

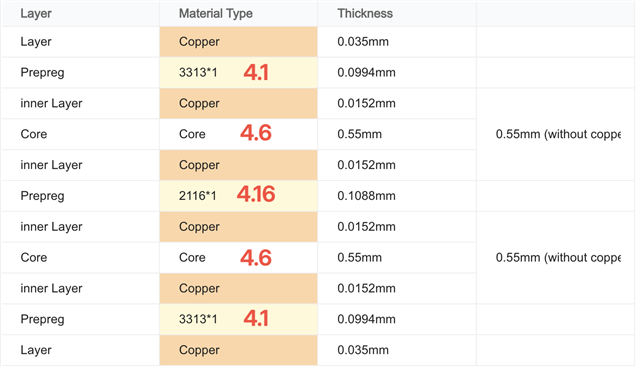

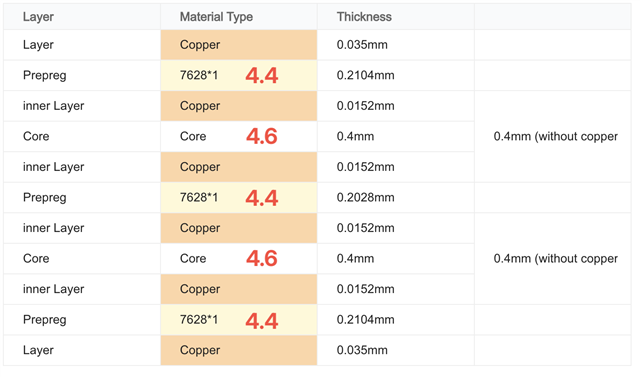

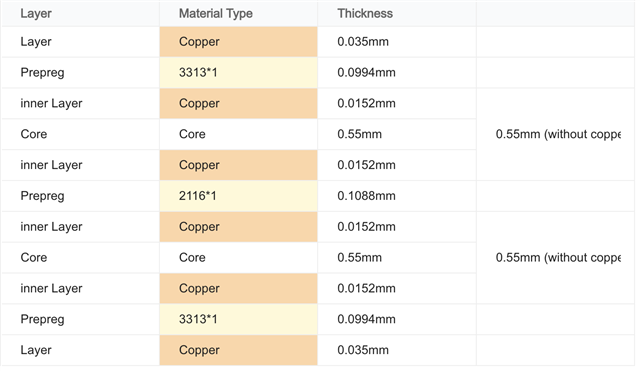

General information on the documents and forum is to use recommended stackup to avoid performance degradation.

however, i read that whole point of AOP is relaxed pcb requirements as antennas are on package.

i was wondering what is minimum i can get away with for prototyping / initial small manufacturing WITHOUT ANY performance degradation.

Please bare with me as i am quite new to this.

Is any of below sufficient for stripped down version of reference design ?

Thank you in advance for your help.