Other Parts Discussed in Thread: , UNIFLASH, SYSCONFIG

Tool/software:

Hi,

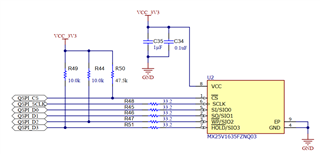

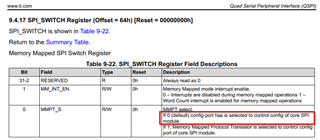

I'm working on a simple application that uses QSPI communication. I'm not using the memory-mapped protocol translator; instead, I'm configuring the core SPI module directly.

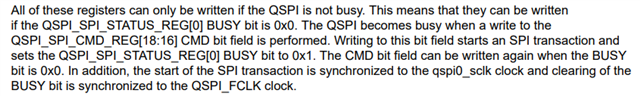

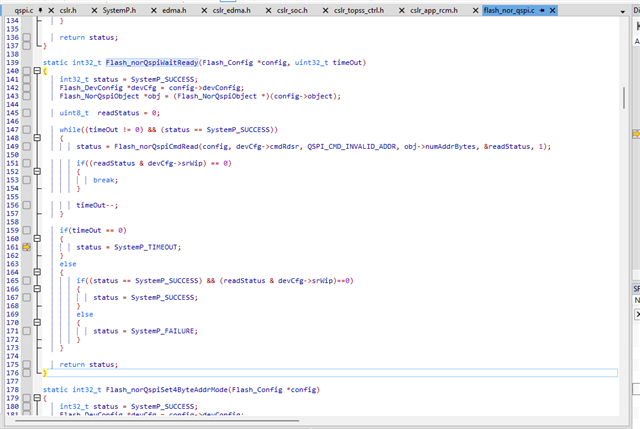

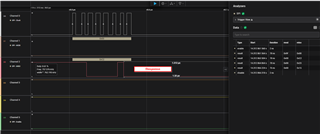

I'm encountering an issue when reading data from the QSPI flash. Transmitting works fine, and I can see on the logic analyzer that the flash device responds with data. However, the SPI_DATA register contains 0x00000000 at the end of each transaction.

I've tried using both Mode 0 (CKP=0, CKPH=0) and Mode 3 (CKP=1, CKPH=1), but the issue persists in both cases.

Has anyone encountered a similar problem or have suggestions on what might be wrong?

Best regards