Hi All,

I'm Validating my LVDS Logic Implemented in Xilinx FPGA

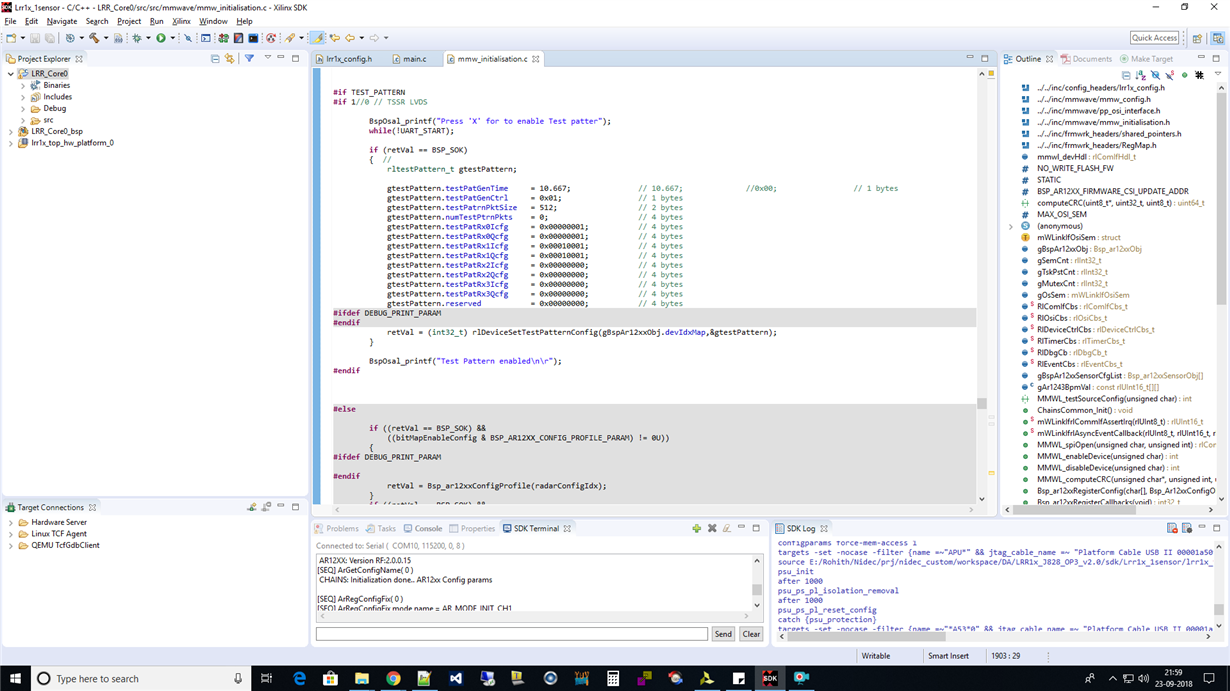

LVDS Data rate = 900 Mbps & My test pattern related setting in mmWave SDK are attached in the below screenshot

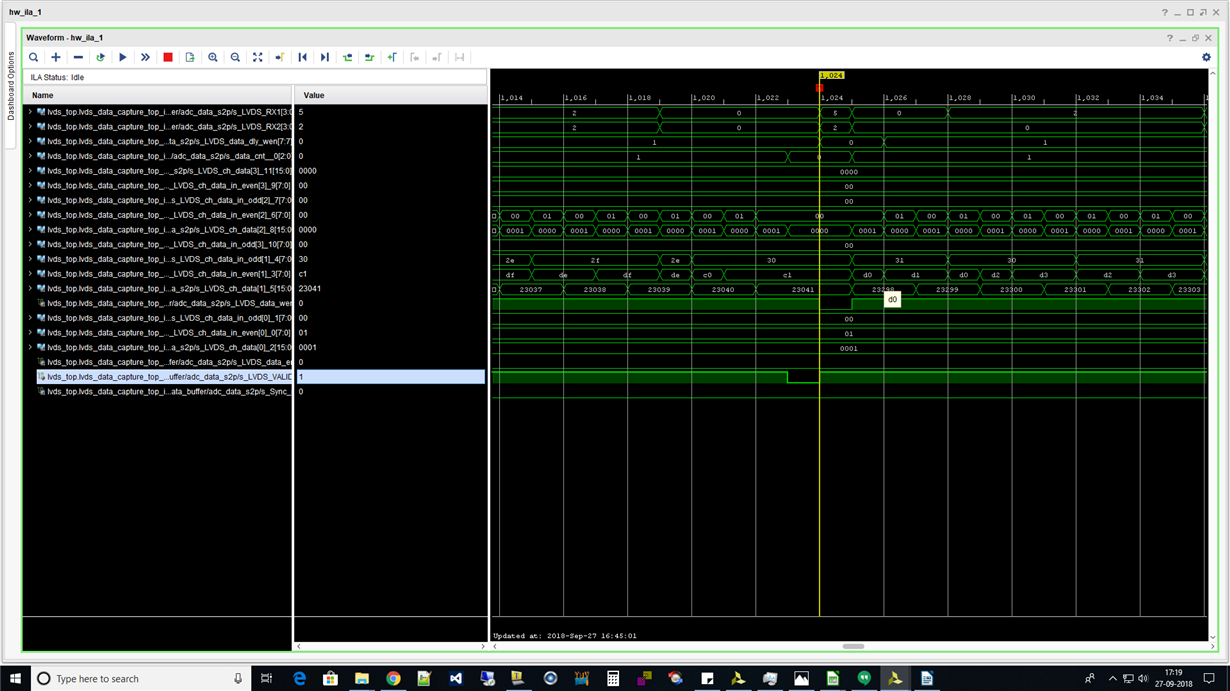

In my Chipscope capture of LVDS data (after serial to parallel conversion), seeing a jump the counter data. at the same time, I'm seeing "LVDS_Valid" signal going low.

The Jump of the counter is dependent on test pattern packet size (tested for 512 or 256)

This can be observed in figure "LVDS_Vivado_Capture1.png" and LVDS_Vivado_Capture_Analysis.xlsx" (data captured multiple times)

My Question is

1. Is this Behaviour expected? If not what could be the reasons.

2. Can this be a C-buff Overflow?

3. Do you think any Issue at FPGA? (i'm capturing data signals directly, no buffering)

LVDS_Vivado_Capture_Analysis.xlsx

Thanks In Advance

Rohith