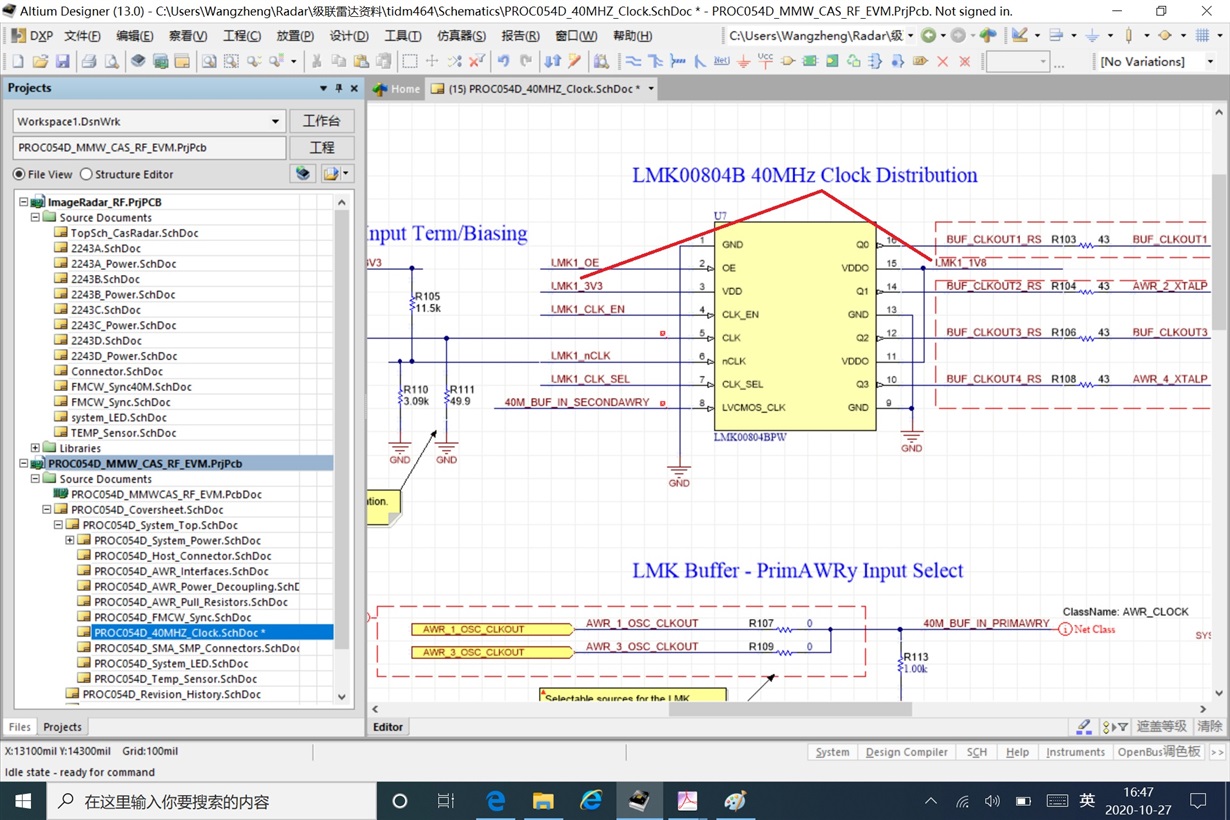

Other Parts Discussed in Thread: AWR1243, TIDEP-01012, LMK00804B

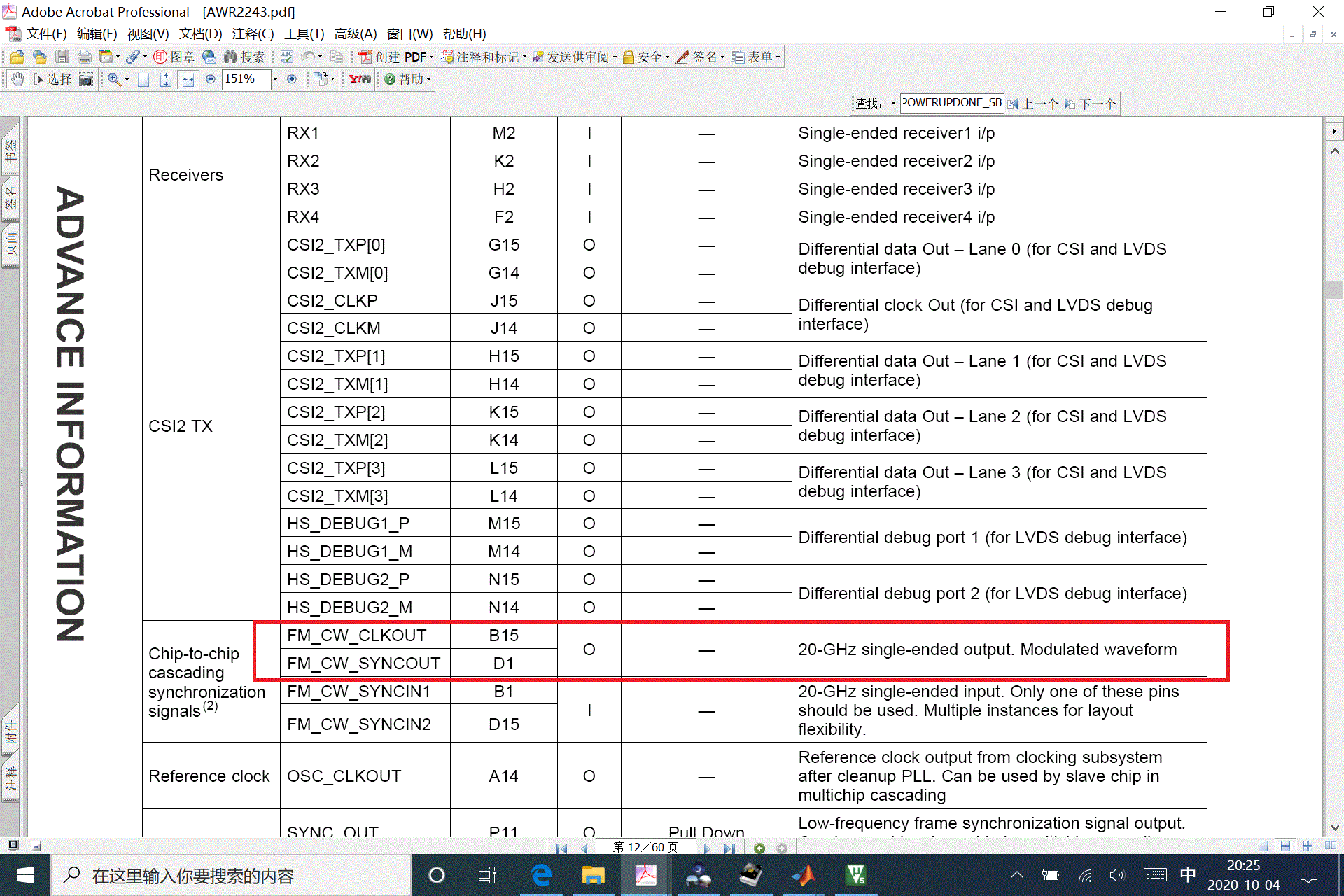

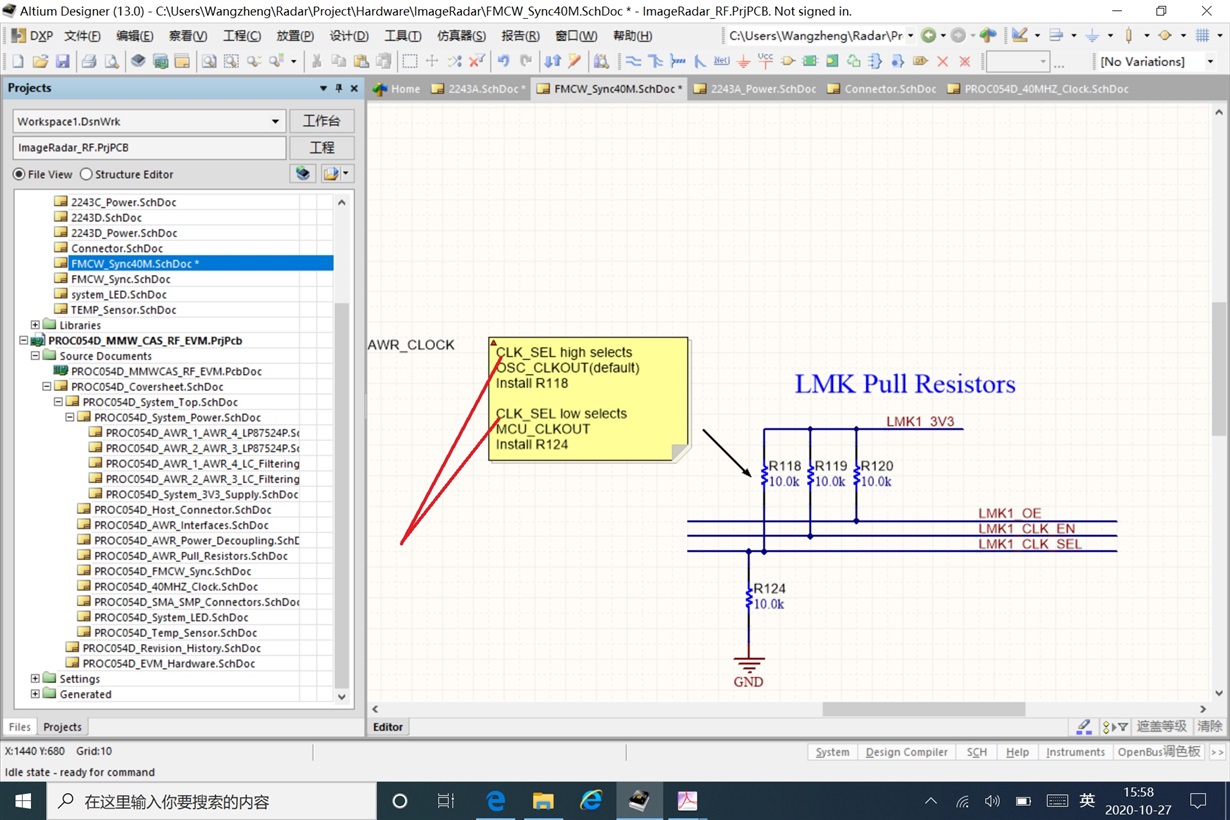

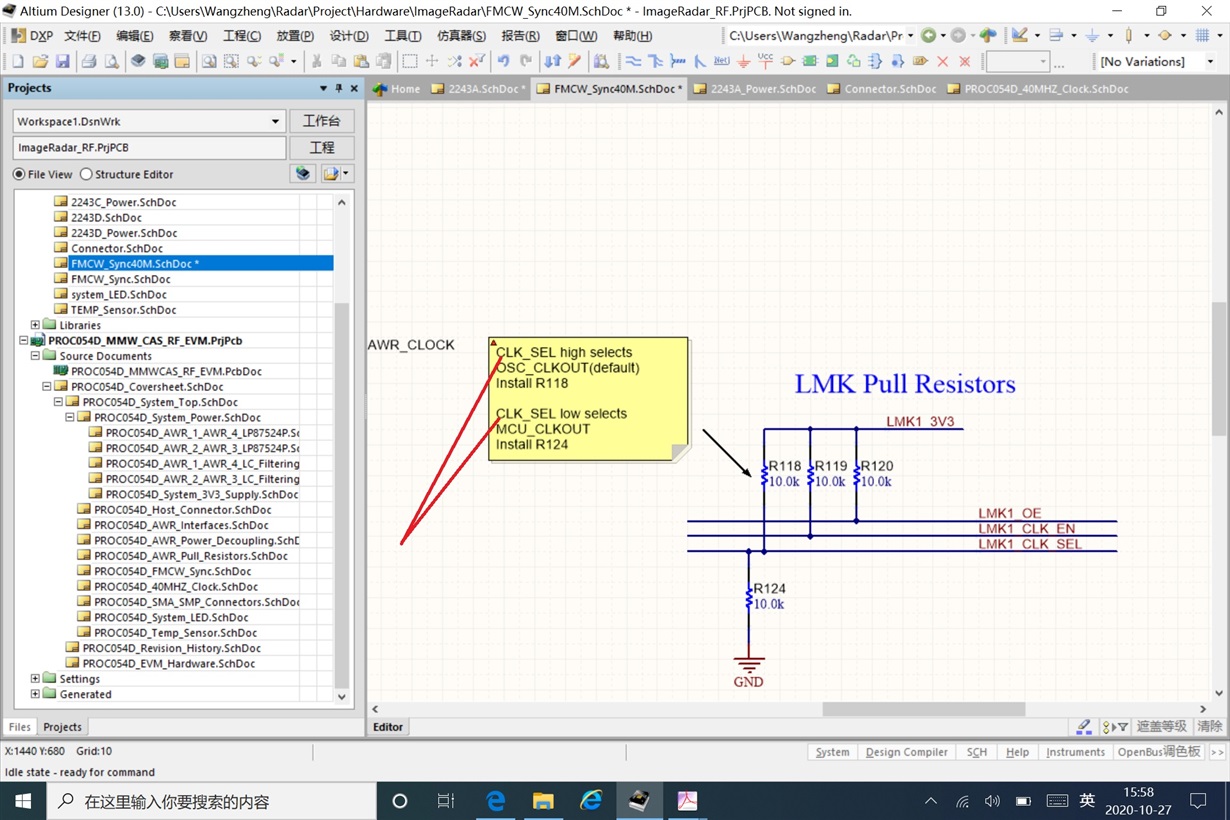

hello, I am designing one image radar and evaluate AWR2243, I download some materials from TI website about AWR2243, but I can't find the detailed Regmap_Appendix,could you provide it to me, so I can read register and configure it through SPI to realize the function I want?

just like the attachments of NXP provideTEF810x_User_Manual_Regmap_Appendix_v0.22.pdf