With reference to this thread on where the original resets are ghosted to bootloader : https://e2e.ti.com/support/sensors/f/1023/t/850397

I have some trouble reading / getting the results. What I get.

My board is always powered, as otherwise I will lose the USB com port. so.

1. After flashing my image and pressing nrst button , SPARE9 is :

0x00990099 , current == previous == NRESET. All good.

2. After executing call SOC_softReset, which does CR4 only reset, I get SPARE9:

0x00990099 , current == previous == NRESET. Same as after button reset.

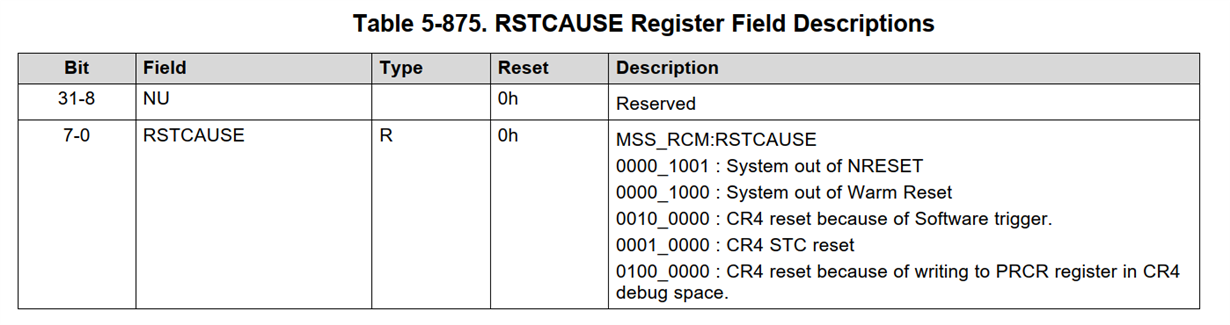

Should I not be getting "0010_0000 : CR4 reset because of Software trigger. " Into the current mssRCM->RSTCAUSE ?

3. With watchdog enabled, after executing SOC_triggerWarmReset, which should issue warm reset , I get :

0x028a028a , and have few questions here :

- With system originally out of NREST (by button), I expected 0x00990028a , i.e. the memory effect. Why is it not here?

- The 0xa = MSS topRCM reset due to MSS WDOG ok, but

0x028 = 0010_1000 == ?? for mssRCM what is this value? I don't see this bit pattern on the link referred to above on SPARE9, or from the Tech Ref manual for x1642.

4. Also, the manual has these extra for Top RCM causes:

"1100" Warm Reset because of Soft trigger SOFTSYSRST

"1000" External Warm Reset

When / which conditions I'm suppose to be seeing these?

5. Manual & SPARE9 values contain these :

...

0000_1000 : Warm Reset

0000_0010 : MSS only Wdog Reset.

0000_0100 : MSS subsystem reset because of Software trigger.

0010_0000 : CR4 reset because of Software trigger.

1000_0000 : CR4 only Wdog reset

....

I don't seem to get any "warm" resets; Is there difference between CR4 only Wdog reset and MSS only Wdog ( is there any other usable wdog on MSS side, besides one in RTI? Does CR4 has it's own internal wdog? );

And when should I expect to see otthers - what to trigger to get them.