Other Parts Discussed in Thread: MSP-EXP430F5529LP, BOOSTXL-PGA460, , PGA460, MSP430F5438A, ENERGIA, MSP430F5529

Hi, team

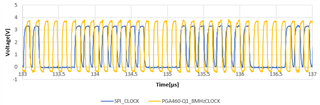

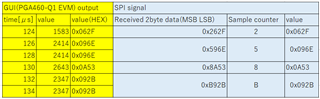

I measured digital raw data from PGA460-Q1(BOOSTXL-PGA460) using MSP-EXP430F5529LP and PGA460-Q1 EVM.

(PGA460-Q1 Datasheet p47-48)

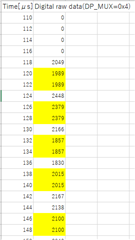

However, I confrimed the same value in a row about ADC data(DP_MUX=0x4).

The same thing happened in BPF data(DP_MUX=0x3), Rectfiler data(DP_MUX=0x2) and Peal Hold and LPF data(DP_MUX=0x1);

Sampling cycle is 2μs/sample(SAMPLE_SEL=1).

Are these digital waw data normal?

Why did this thing happen?

regards,