Other Parts Discussed in Thread: TMUX1108

Hello,

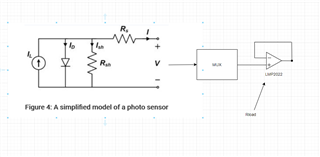

I'm using the CD4051B for a precision sensing application where multiple reference resistors are multiplexed into the reference pins on an ADC.

Channels 0-8 connect to the high side node of the reference resistors and the common node goes to a zero-drift op-amp used as a buffer before driving the Vref pins of the ADC.

The excitation currents for the RTDs will be in the 10s of microamps, and so I need to account for all error sources.

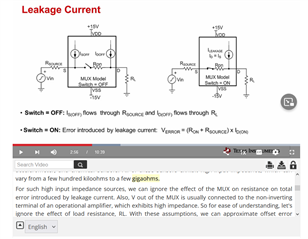

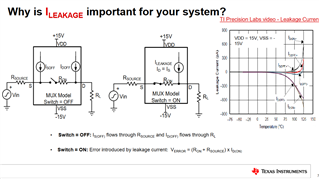

I have read from a TI presentation that leakage current will act as a current source to either the input or out and create an offset based on the load or source resistance:

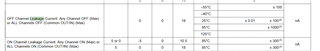

However, this doesn't seem right for this IC as the datasheet states:

If the TI presentation is correct then i would have to multiply the leakage current by an extremely high load resistance which is made up from the input impedance on the buffer op amp itself.

Should i be concerned about leakage even if the buffering make the circuit extremely high impedance?