Other Parts Discussed in Thread: TMUX1111, TINA-TI, TMUX1112, TMUX6104

Hi Texas

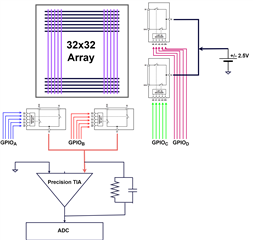

I am looking for a sensor crossbar array (32x32 ie 32 rows and 32 columns) characterization with time-multiplexed fashion.

Our sensor current which passes through a specific channel (say 1st channel at particular time) of TMUX1108 will vary from 0.1 nA to 100 nA. For safe operation, I have the following queries.

- Can I operate the TMUX1108 IC with +/-2.5 supply for rail-to-rail operation ie for input analog of +/-2.5V range or some headroom is required?

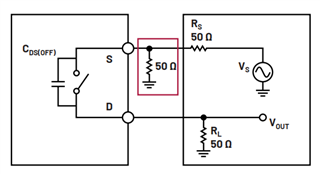

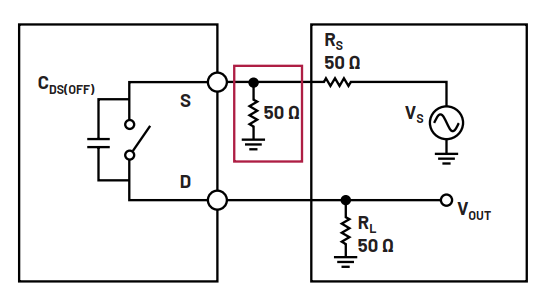

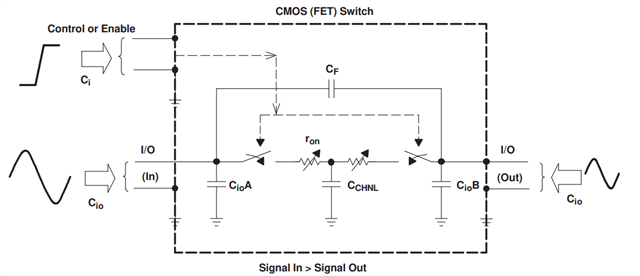

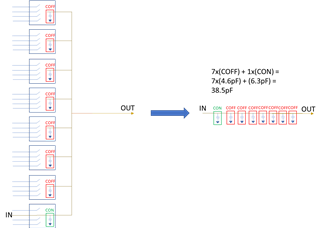

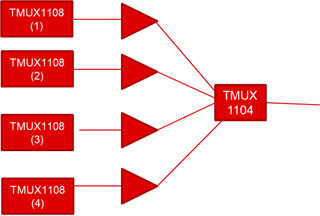

- For minimum leakage, and minimum capacitance/parasitic, we are using four TMUX1108 IC to probe 32x32 sensor array (image attached). By mean of enable pin and GPIO we want to characterize (in a time multiplexed manner) a specific sensor among 1024 possible positions in 32x32 crossbar architecture. As attached, will there be any offset/interference/perturbance in multiplexer output if we short D pins of four TMUX1108 (1:16 MUX is shown for representation purpose) and further gives to the input of transimpedance amplifier for measurement of 0.1nA to 100 nA?

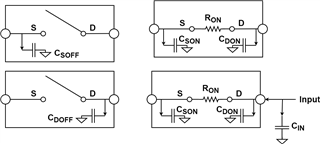

- At constant temperature and +/-2.5V can we assume that Ron = 125 ohm and 1.5 pF OFF capacitance?

- Could you please clarify in detail where exactly these capacitances [CS (Off), CD (Off), CD, CS (On), CIN] are building up when we connect D pin to any of the selectors say S1? For your reference I am attaching one more image, kindly evaluate that.

Thanks and Regards,

Deepak