Hello dear friends,

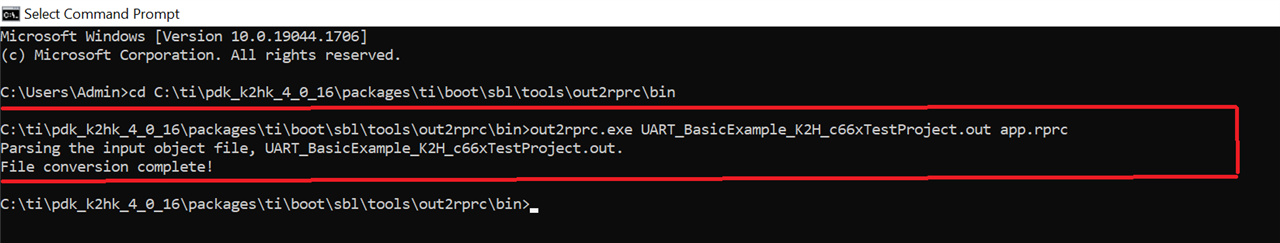

I want to make loadable image files of .out application to write on the EVMK2H board. as described in the link (https://software-dl.ti.com/processor-sdk-rtos/esd/docs/latest/rtos/index_Foundational_Components.html#k2h-k2e-k2l), I generated two files with these commands:

- out2rprc.exe [.out file] [rprc output]

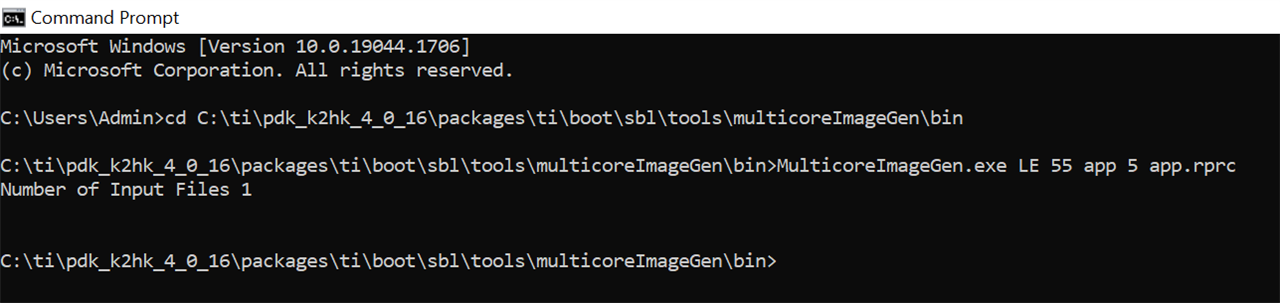

- MulticoreImageGen.exe LE 55 [output name] 0 [rprc output]

then I'm using the file generated from the second phase:

I connect to the board

connect to the arm core and initialize it

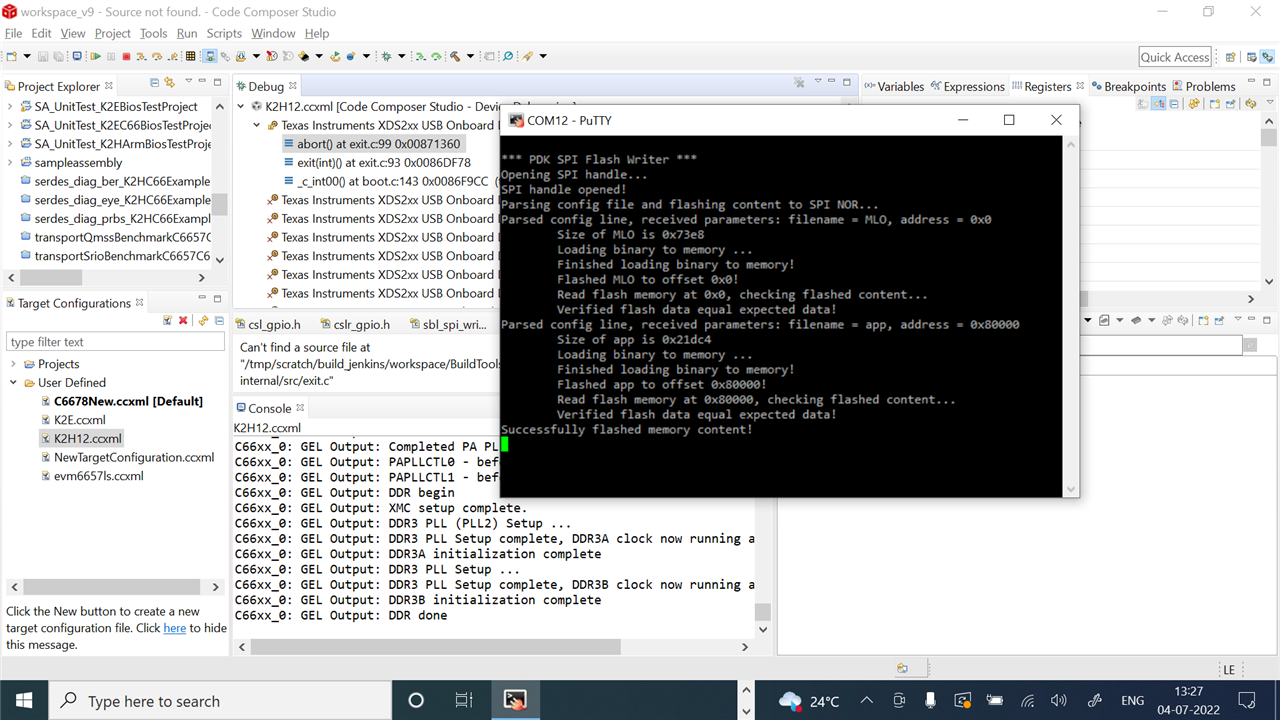

connect to the DSP core 0 and load the spi_flash_writer.out

and here with the example nor boot example, it works fine and example is written successfully on the board but it cant write our main application and got error like below:

*** PDK SPI Flash Writer ***

Opening SPI handle...

SPI handle opened!

Parsing config file and flashing content to SPI NOR...

Parsed config line, received parameters: filename = multicore_generated, address = 0x80000000

Size of multicore_generated is 0x91464

Loading binary to memory ...

Finished loading binary to memory!

Error flashing memory! Error code -3

Error parsing config file!

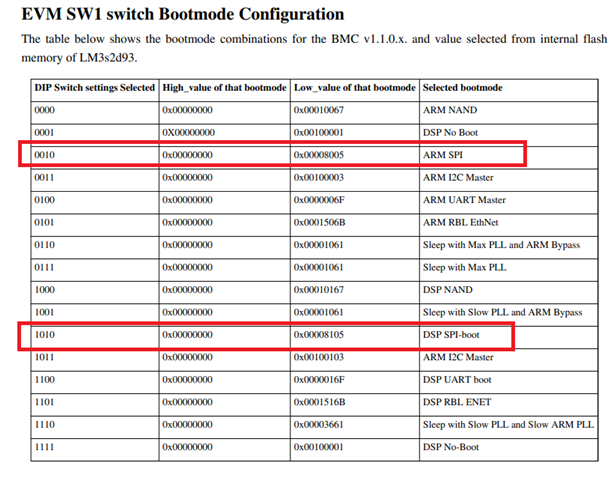

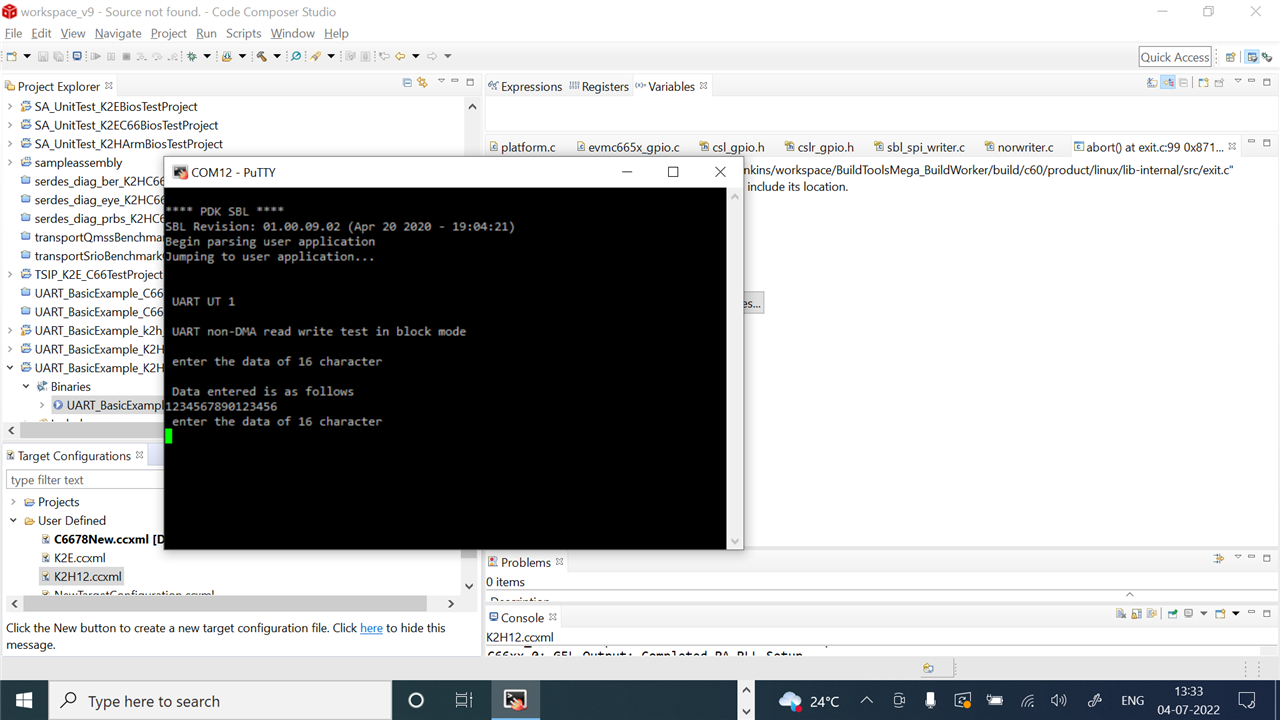

even when I try to write to memory address 80000 it going to be successful, but my program won't run after putting the dip switch on the spi nor boot and restart the device.