Hi

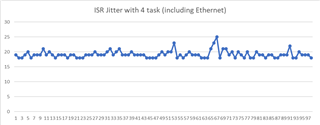

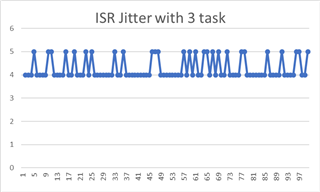

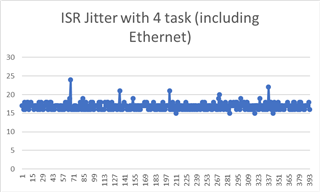

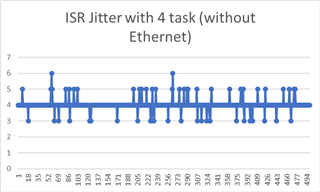

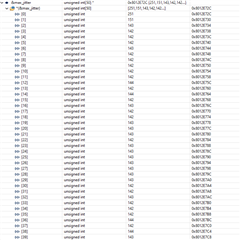

We suffer from unexplained jitter in FreeRTOS (Cortex R, core 0).

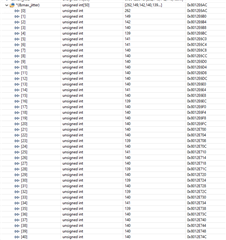

Measurement method:

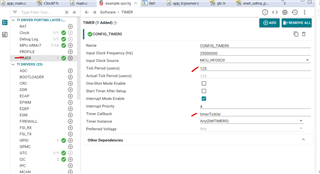

- Periodic interrupt, once at 500 uSecs

- ISR posted a binary semaphore to task (at highest priority)

- Tasks wakes up and samples CPU time stamp counters.

Differences are used to assess system jitter.

Simple example, one task, jitter within 2-5 uSecs. Good.

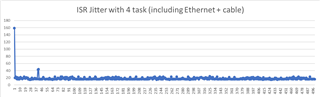

It looks like latency grows when I enable more parts in software, plus some factors that I cannot explain.

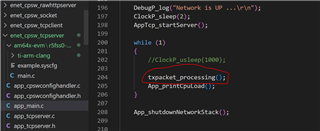

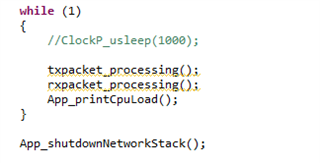

No access to hardware. Low priority tasks wake up periodically, but do nothing.

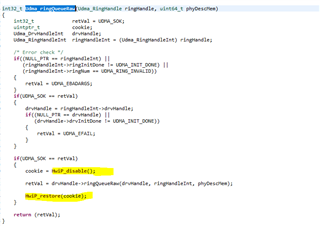

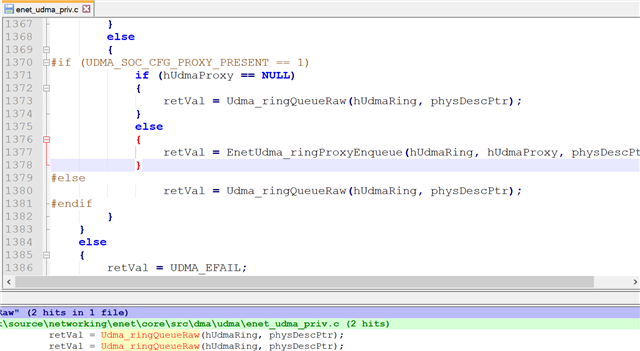

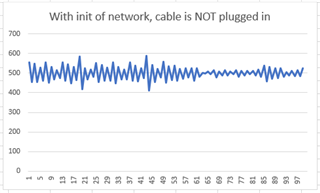

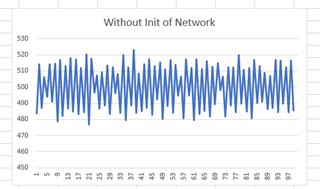

For example, there is big difference in latency with and without initilization of network code.

Without init of network, latency/jitter is +/- 20 uSec, with init of network, but cable is disconnected (no interrupts from DMA) +/- 80 uSec.

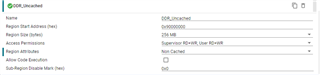

All code run from DDR, DDR is cached.

Cache miss can explain such a behavior?

Any thoughts ?