Other Parts Discussed in Thread: OMAPL138, OMAP-L138

Tool/software: TI C/C++ Compiler

Hello,

I have some structs in my project for which I need to use the "packed attribute" of TI ARM compiler.

Until now I did not find any solution or setting that works.

Here is my environment:

Processor: OMAPL138E

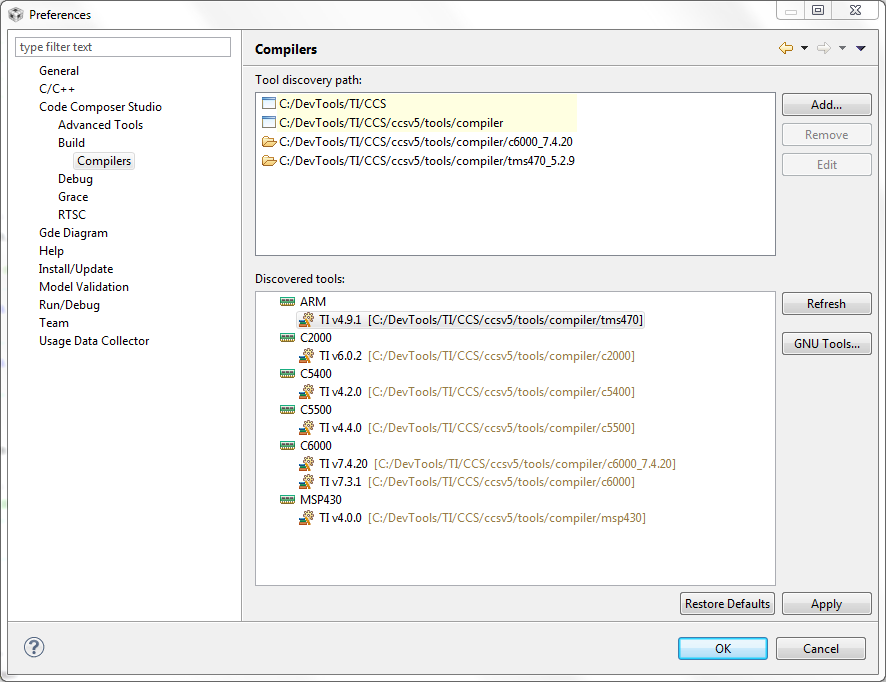

Code Composer Studio Version: 5.1.1.00028

ARM Compiler Version: TI V4.9.1 (configured for variant "Genreic ARM9 device")

In this forum I already found some posts like this

https://e2e.ti.com/support/tools/ccs/f/81/p/38211/196004#196004

so I enabled "--unaligned_access=on", but there is still a compiler warning:

#1176-D the "packed" attribute is ignored in a typedef.

So my questions are:

- Does the toolchain (mentioned above) support the "packed attribute" for my Processor type (OMAPL138)?

- If yes, which additional compiler settings could be relevant for this?

- If not, is there a TI ARM Compiler version which does support this?

Thanks in advance for your support!

Best regards,

Markus

Here is an example ("packed" did not work - that means this struct is compiled with a 32Bit alignment):

typedef __attribute__ ((__packed__)) struct EPL_IRES_FRAME_Ttag

{

uint8_t bMtyp;

uint8_t bDest;

uint8_t bSrc;

uint8_t bSvid;

uint16_t usFlags;

uint8_t bNmtStatus;

uint8_t bReserved;

uint8_t bEplProfileVersion;

uint8_t bReserved2;

uint32_t ulFeatureFlags;

uint16_t usMTU;

uint16_t usPollInSize;

uint16_t usPollOutSize;

uint32_t ulResponseTime;

uint16_t usReserved3;

uint32_t ulDeviceType;

uint32_t ulVendorId;

uint32_t ulProductCode;

uint32_t ulRevisionNumber;

uint32_t ulSerialNumber;

uint32_t aulVendorExtension[2];

uint32_t ulVerifyConfigDate;

uint32_t ulVerifyConfigTime;

uint32_t ulApplicationSwDate;

uint32_t ulApplicationSwTime;

uint32_t ulIpAddress;

uint32_t ulSubnetMask;

uint32_t ulDefaultGateway;

uint8_t szHostName[32];

uint8_t abVendorExtension2[48];

} EPL_IRES_FRAME_T;