Tool/software:

Dear Team,

Thank you for your response to my earlier query. Based on your suggestions and further experimentation, I have made the following observations and have additional clarifications:

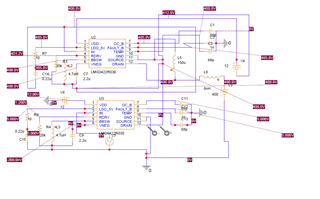

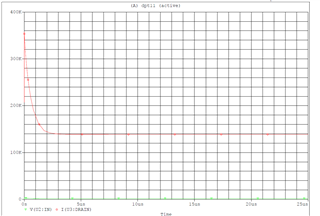

- Double Pulse Test Issue

I have attached my schematic and the results for Vds and Ids for your reference. As per the LMG342xx motherboard schematic, I replicated the setup and added a 10-ohm resistor in series with the 0.22 µF capacitor at the LDO pin. Unfortunately, I still could not achieve the expected double pulse test results. Could you kindly review the setup and advise on any additional changes that might be needed? - Slew Rate Reduction Using Bootstrap

Regarding the approach of reducing the slew rate of the low-side device by turning on Q1 MOSFET with the fault signal of the top FET:- When the MOSFET turns on, the effective resistance at the RDRV pin decreases, which, in theory, could increase the slew rate again.

- Could you please clarify how this method effectively reduces the slew rate, despite the observed change in effective resistance?

- Use of Digital Isolator for H-Bridge

For the H-Bridge configuration, I intend to use the same digital isolator for the gate pulses of both top-side switches. Considering the different switched nodes of these devices, would this approach be feasible? If not, could you suggest an appropriate isolator configuration?

Your guidance on these matters would be greatly appreciated. Please let me know if any additional information is required to assist in resolving these issues.

Thanks and Best Regards

B Raja Sekhar