Part Number: UCC28950

Tool/software:

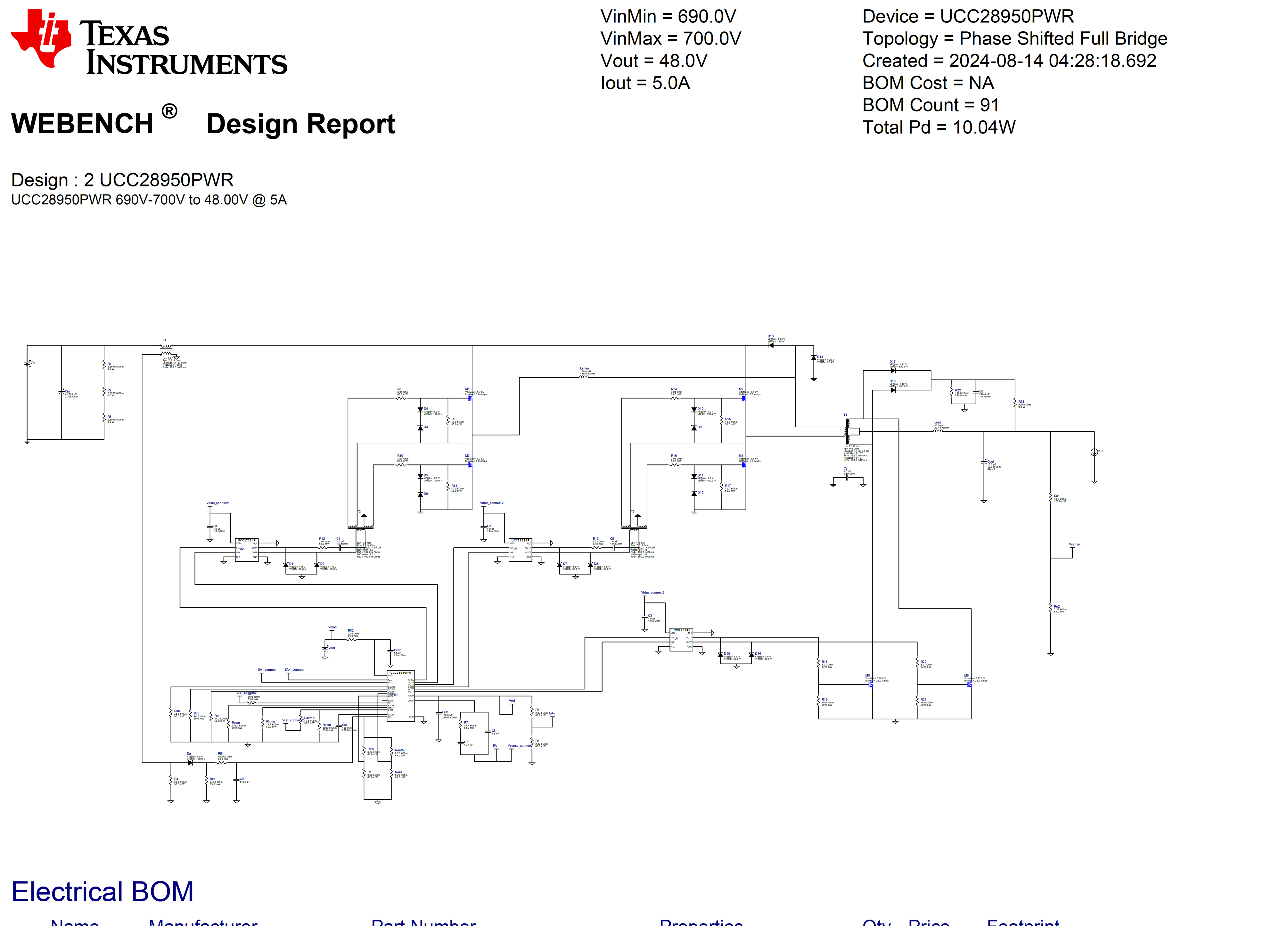

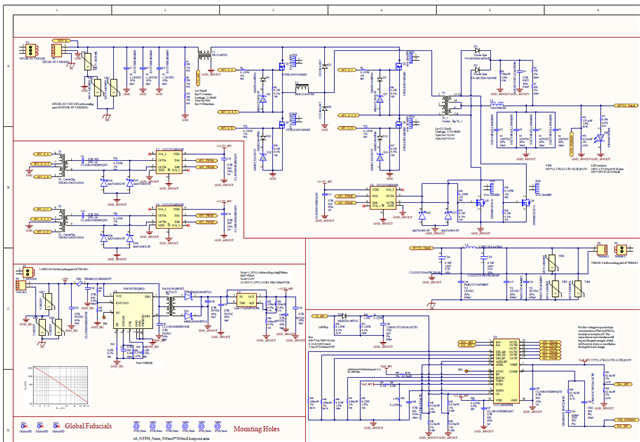

Currently, we are facing a problem with the PSFB design based on UCC28950. The design is 240W, 48Vout, 5A Iout, 700Vin, Fsw 100KHz. In addition, the Tx turn ratio is 12.4:1. I use UCC27324DGNR as gate driver (I highlight here because I published a question before and I cannot reply a wrong answer. So I re-publish this question) to provide two half bridge Vgs (High side is not refer to GND).

--------Q1------Q3 Q5---------|--Vout+

| | TX -------L---|---Vout-

--------Q2------Q4 Q6---------|

If the Sch is blurry, please refer to the EVM design, which is https://www.ti.com/lit/an/slua560d/slua560d.pdf?ts=1738633435221&ref_url=https%253A%252F%252Fwww.google.com%252F

The problem is, in the light load situation, we can get 48Vout. But there is no phase shift for the Vds (Q3, and Q4), so there is no deadband on the Tx waveform. Ideally, when I give 700Vin, based on the turn ratio of the Tx, I can get 53V without control. If I get 48V, the TX waveform should have a deadband, but it is not. After that, I add load, the Vout starts to drop.

So, can you please help us, with why there is no phase shift?

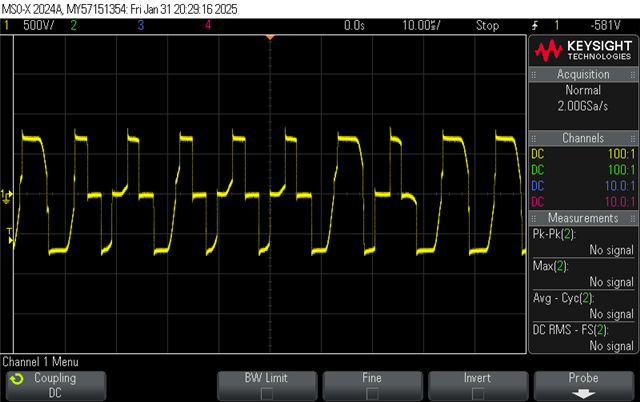

Please see the waveform attached.

The picture below is the Tx waveform, which is damping when the load is only 200mA. When the load is above 200mA, the waveform will become an “H-bridge” with 50% duty cycle.

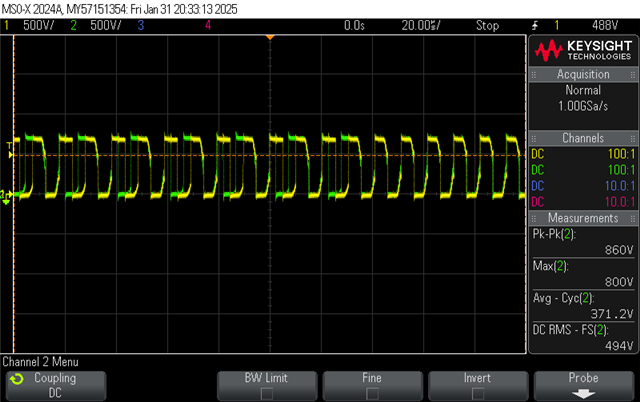

The picture below is the Vds of Q1 and Q4. Yellow is Q1, Green is Q4. This is still on the 200mA load situation. You see the phase shift angle (direction) of Q4 is wrong.

I am very confused why no phase shift (or the wrong phase shift happening). Is that because of Tx or IC set up? Or Tx turn ratio not correct.