Other Parts Discussed in Thread: SFRA

Tool/software:

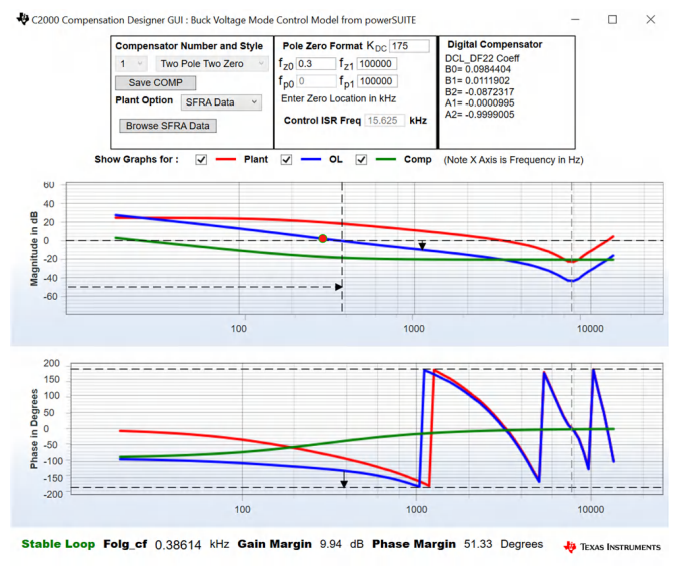

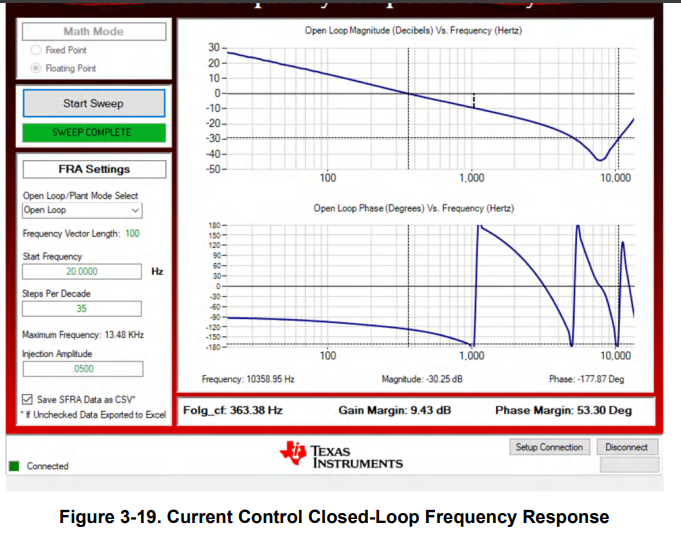

I am planning to implement control algorithm i.e., CC and CV loop. For that I need at what frequency we can implement. Related to this I found one design document of TI related battery tester with two channels. The Document number is: TIDA-010087 (100-A Dual-phase digital control battery tester reference design). I go through this document, in that initially they find the frequency response of the plant, at this time the phase margin obtained as 6.66 Deg. Generally, the phase margin should be >45 Deg. Then we can tell system is stable. To increase the phase margin in that document they added the 2pole and 2zero compensator. At that time, the frequency mentioned as 15.625kHZ and the phase margin is 51.33 Deg. The same frequency is considered for the Control loop implementation(CC & CV) and ADC sampling frequency.

My Doubt is the frequency mentioned is compensator tuned frequency or plant + compensator tuned frequency. Please clarify that my understanding is correct or I need to analyse in different way.

After that again frequency response is shown and mentioned as open loop, that means compensator and plant in open loop is obtained and check the phase margin and all. Is it correct.?

In the same way I also tried to implement using MATLAB Software. Initially current to duty cycle transfer function obtained bode plot is implemented from that I obtained phase margin as 4.74 Deg. After that my transfer function is converted to continuous domain to discrete domain at my switching frequency. Then I implemented sisotool in MATLB to design the compensator. In compensator editor I added the 2-poles and 2-zeros to the system and tuned the compensator by adjusting the Gain and the phase margin obtained is 45 Deg and that time my frequency is 6.78kHZ. So I need to use this frequency as the control loop frequency and ADC sampling rate or the compensator obtained from the MATLB should add to plant and the overall transfer function should implement the bode plot and obtained the phase margin and frequency. This overall obtained plant + compensator frequency should I use for control loop frequency and ADC sampling rate.

Please clarify in my approach to design in better way.