Other Parts Discussed in Thread: CC1352P, TPD1E04U04

Tool/software:

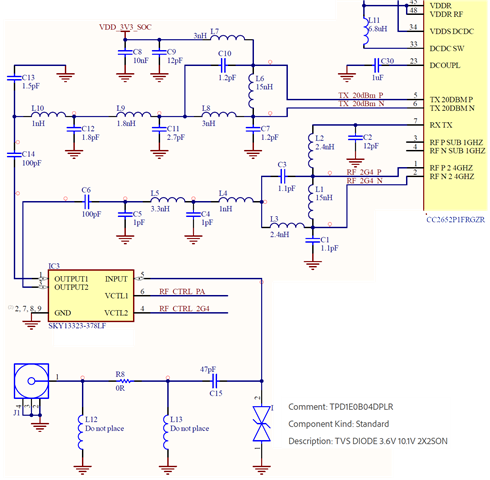

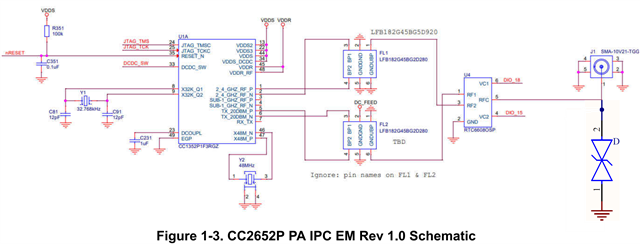

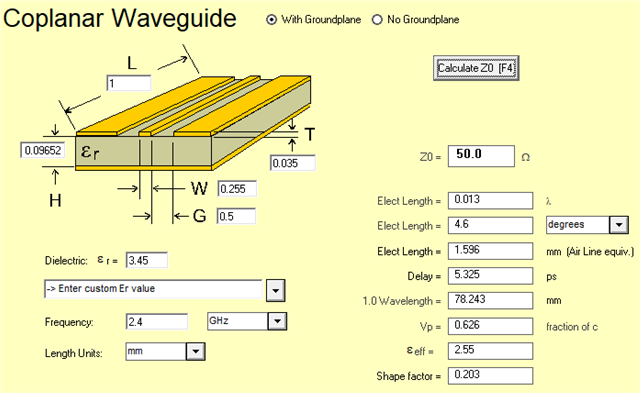

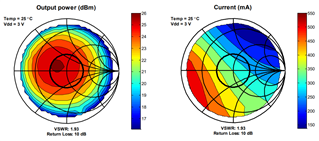

I’m currently reviewing a legacy design for BLE 5.2, 2.4GHz (schematic attached) that may be experiencing issues related to impedance mismatch, sensitivity, or low output power on both RF ports (low power and 20 dBm). The antenna in use is a Taoglass PC.11.

Can anyone confirm whether the selected matching component values are optimal? Should an Integrated Passive Component (IPC) be used on both RF ports? If so, what IPC is recommended for the CC2652P, particularly for the 20 dBm high-power port?

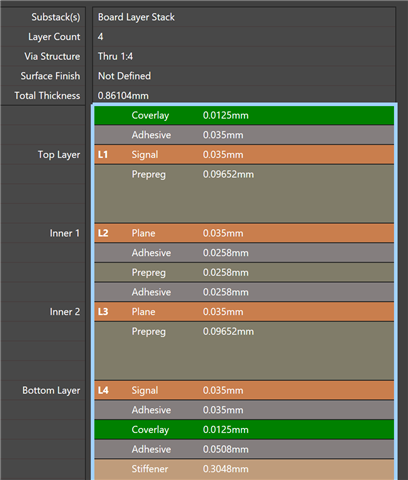

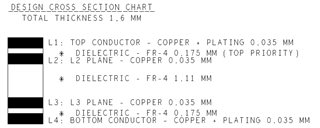

I can also share the PCB layout if needed. An S11 analysis using a VNA and output power measurements with a spectrum analyzer are planned.

Thanks for answering.