Tool/software:

Hi There,

In the App note, Crystal Oscillator and Crystal Selection for the CC13xx, CC26xx, and CC23xx Family of Wireless MCUs (Rev. L)

the -R vs. C load is Inverse-square, shows in equation (7).

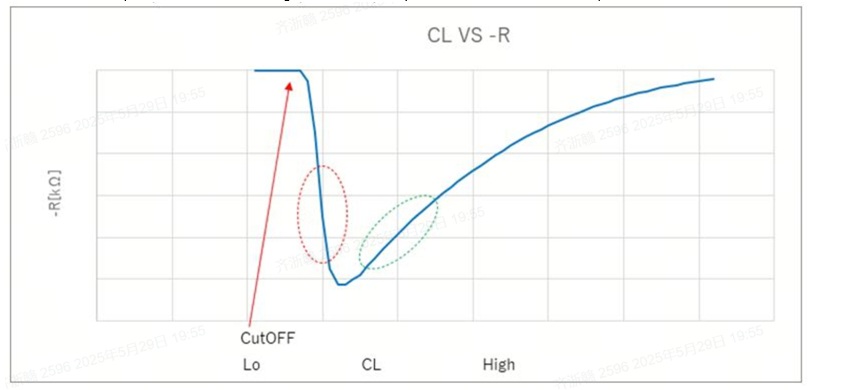

But customer asked crystal vendor, they shows below curve. maybe the equation 7 meet part of the curve by ignore some other coefficient.

could you please share more than the equation's curve? what's the TI's cutoff number?

BR. Albin