Other Parts Discussed in Thread: TRF7970A

Hi,

we seem to have a similar problem as the original author of the linked discussion, albeit with a slightly different IC.

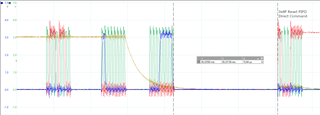

An ISO15693 command sequence completes successfully with Irq_srx interrupt, but the following query of the FIFO status register yields zero bytes to be read. The problem persists for any subsequent commands.

Just as described in the related thread, not all of our PCBs show this behaviour but we see a failure rate of about 30 %. This problem can be reproduced and resolved by powercycling the IC.

We have tried every trick in the book to avoid this issue by means of configuration changes, reinitialization and application of generous wait states in all imaginable places but nothing seems to be working so far.

The original discussion unfortunately does not present an explanation or a solution to this problem and we're still curious whether this issue can somehow be resolved.