Other Parts Discussed in Thread: LP-EM-CC35X1,

Tool/software:

Hi Team,

I am working on a board based on the LP-EM-CC35X1_RevE3_DesignFiles and have CC3551E on it.

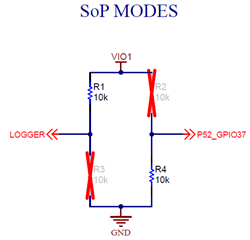

Could you provide details on the SoP modes defined by the LOGGER and P52_GPIO37 pins? These are not mentioned in either the datasheet or the TRM.

Thanks in advance for your help.

Best regards,

Robert