Dear Sirs,

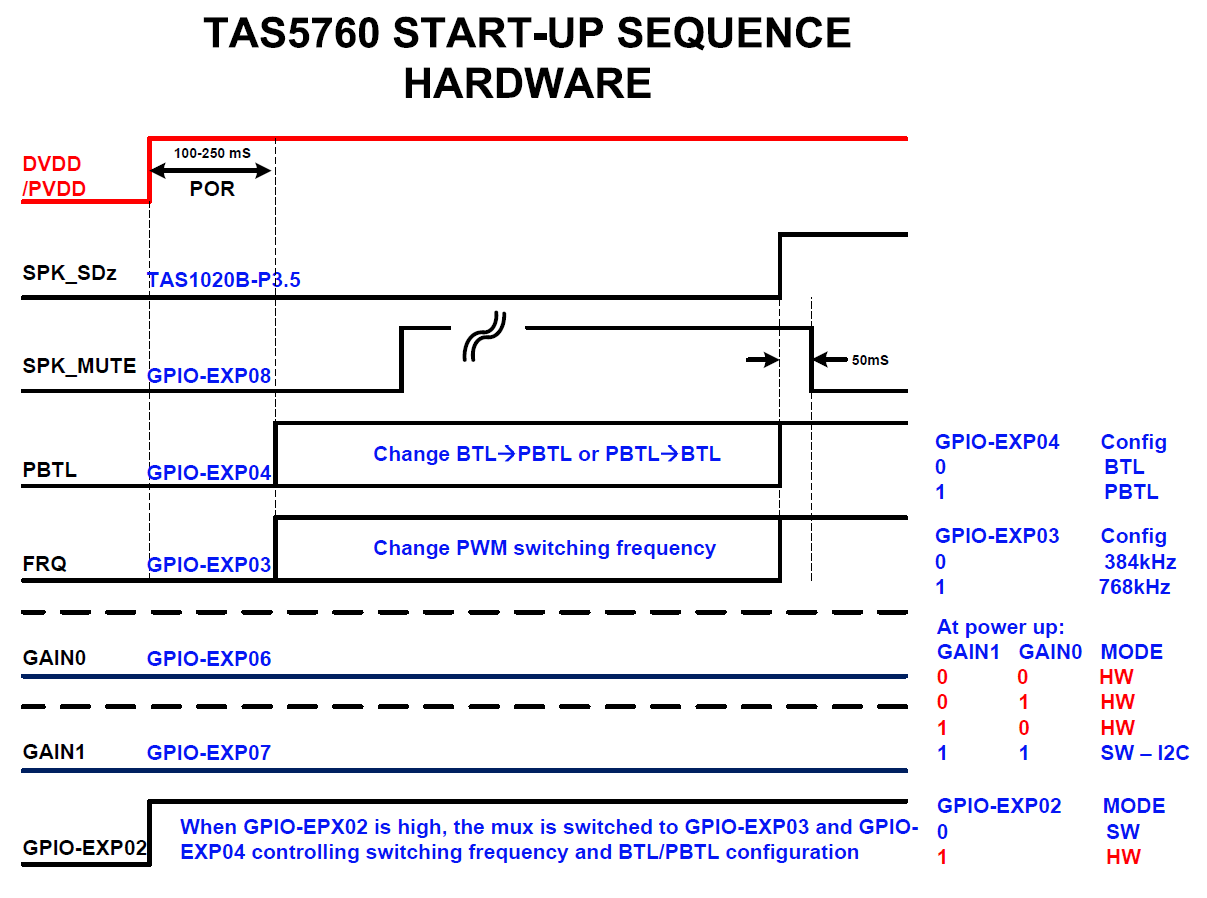

My customer asked us about Power on/off Sequence of TAS5760M for hardware control.

There is a phenomenon which is not output at power on of his board.

At that time, ANA_REG is 10 V and it is abnormal voltage. (Normal is 3.3V)

Therefore, I think that there is a factor in the power ON / OFF sequence.

Do you have what can be thought of as a cause in such a case?

His power on sequence is as follows.

1.After turning on the power supply, set SPK_SD to Low and SPK_SLEEP / ADR to High.

2.After the power supply is stabilized and the hard control pin is set, set SPK_SD to High.

3.After releasing shutdown, set SPK_SLEEP / ADR to Low and about 3 seconds after SPK_SD becomes High SPK_SLEEP / ADR is released.

Is this correct?

The power off sequence is

SPK_SD is LOW after SPK_SLEEP / ADR is HIGH and output OFF after the power is turned OFF.

Is this correct?

Best Regards,

Y.Hasebe