I have a problem regarding DDC316. I have tested two chips and both behave similar.

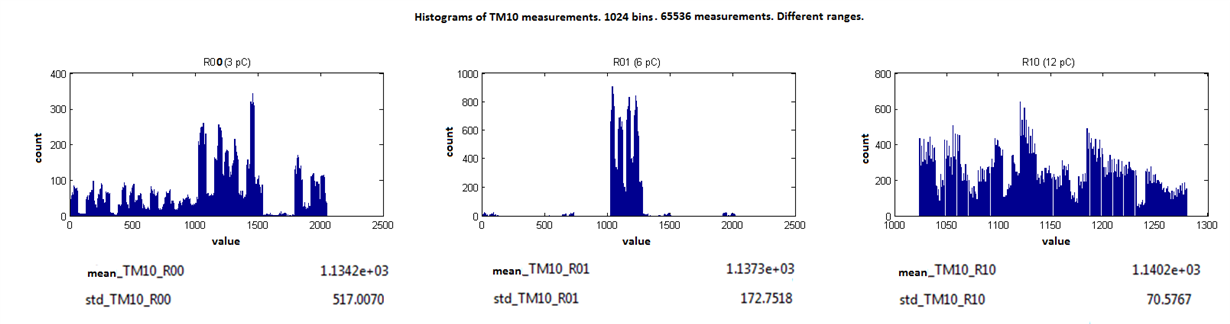

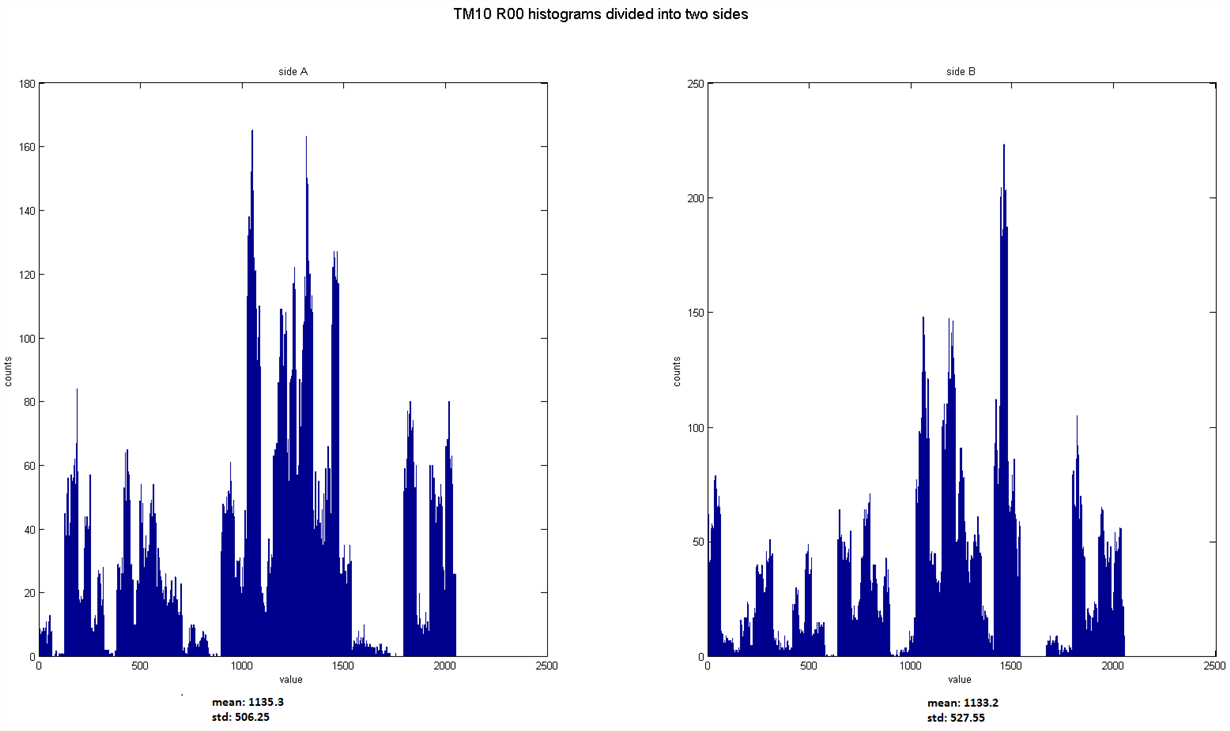

I wanted to test the chips in TM01, TM10 and TM11 modes (each TM in all ranges - from 3 to 12 pC). I have gathered many data in each mode (eg. 65536) and created histogram of the collected data. What surprised me is that the standard deviation is relatively high. Below is an example of the TM10 test. Please look closely at the R01 (R00 is similar) histogram. Besides values around the mean value there are some peaks from 0 to 2000. RANGE[10] (12 pC) looks completely different and the standard deviation is acceptable.

Basically what I expected from the measurements was gaussian shape of the histograms. It is not only not gaussian, but there are values that are far from the real one (but average value from many data is correct). Without averaging the measurement error is high.

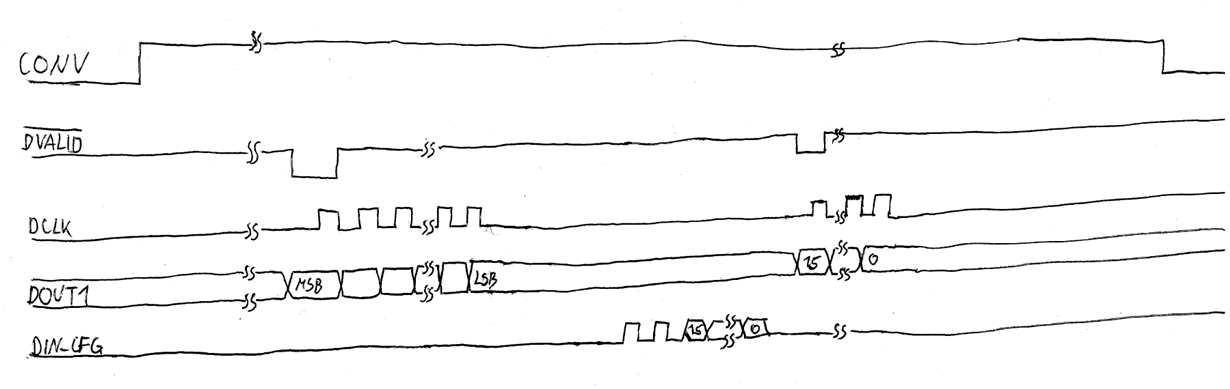

Has anyone had similar problem? I can provide detailed information about DDC316 configuration if needed.