Dears

when customer use the AFE430EVM for debuging and their own designing, they find that some of the register write a value, and then reading it , the value changed. such as below example. pls. help to give the reason. thx

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Dears

when customer use the AFE430EVM for debuging and their own designing, they find that some of the register write a value, and then reading it , the value changed. such as below example. pls. help to give the reason. thx

Hi Prabin

Thank you for your patience.

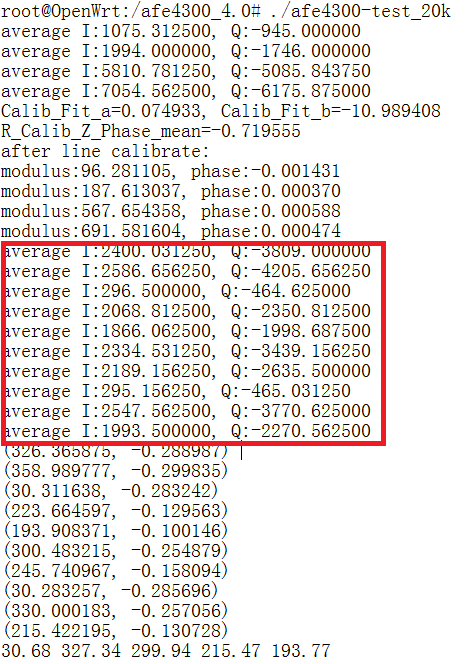

I have another question is that when I the IQ rules changes(same MCLK, same frequency-division), I will do calibration and calculate other channels impedance, but

calculated impedance have a little difference between different IQ rules. Some IQ rules, the difference are big.

Can you provide a calibration algorithm, Thank.

Best Regards

Hi Weiteng,

Here is the simple calibration algorithm.

After implementing this algorithm can you please share values following for each IQ rules

Regards,

Prabin

Hi Prabin

1. I'm not sure if my algorithm is correct. In my algorithm model:

a. impedance _modulus = a * sqrt(I^2+Q^2) + b (a & b use four known impedance to calculate)

b. impedance _phase = atan(Q/I) - c (c use four known impedance to calculate)

*The data use my algorithm model as above. And my four known impedance value is (96.35, 187.54, 567.62, 691.62).

2.In your algorithm( Y = MX + C), Is it just about the calibration of the modulus of resistance? And what about phase.

It seem that our algorithm about modulus is same.

3.Please help me to analysis why unknown impedance have bigger difference in different IQ rule. Thank you very much.

Best Regards

Hi Weiteng,

Basically we have same algorithm, even for my case you can find phase from calibration resistors and subtract it from unknown resistors's phase.

To understand your data can you please tell me why the I/Q values are changing as shown below ( marked in RED)?

Is it for different IQ rules, if yes share the BCM frequency (as well as IQ Demod frequency) for each of those.

Can you also measure the voltage across the unknown resistors using the oscilloscope? For different IQ rules, the frequency will change but swing should be same.

Regards,

Prabin