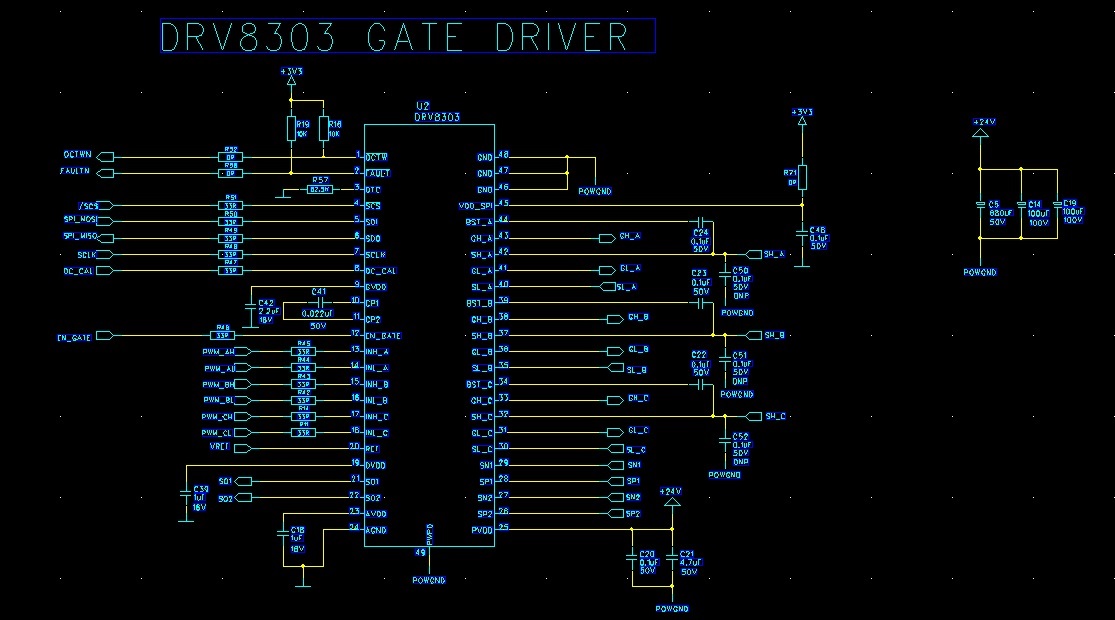

We are trying to configure the Control register 1 of DRV8303 with the hex value 0x128A. We are operating on Current limit mode.

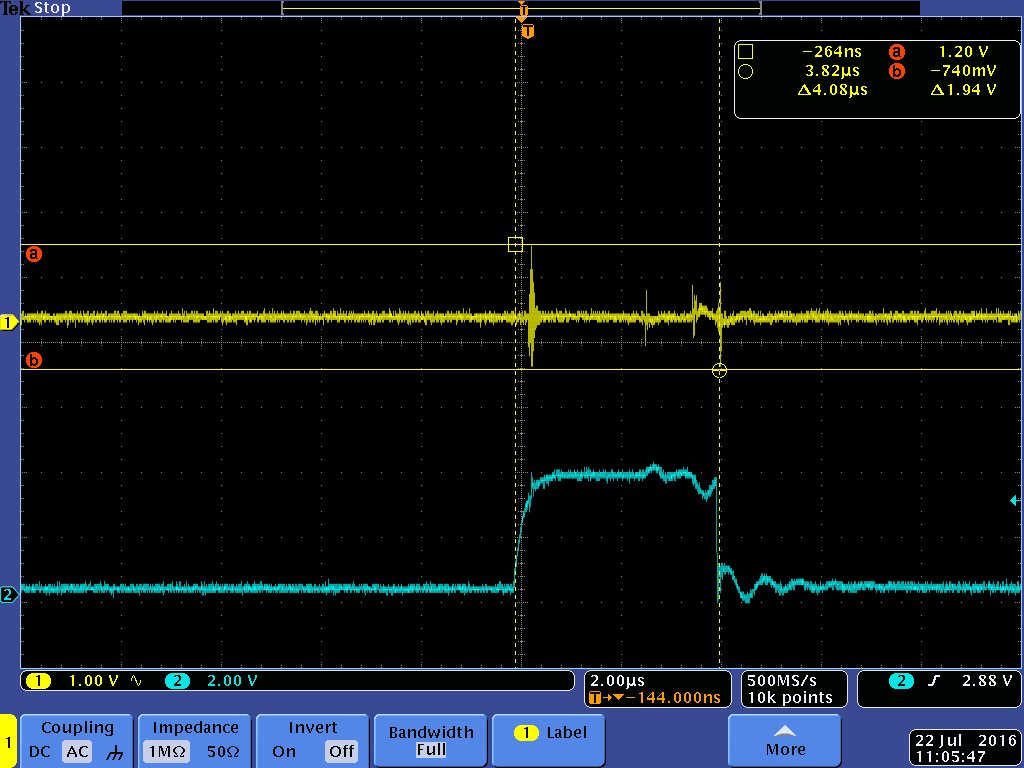

We have observed that for once it configures the CR1 correctly and we have verified it by reading back the value from the DRV8303 IC.

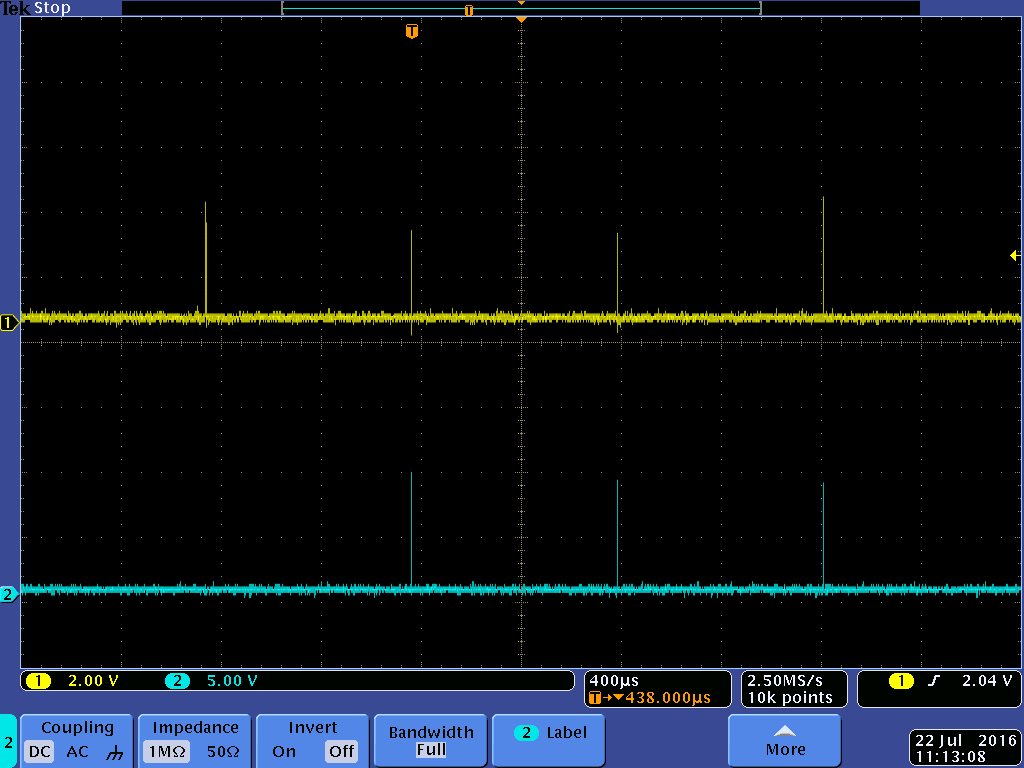

But once we read-back its successful configuration(which is read only once) , if we try to continuously read-back the configuration from the DRV8303 we find its configuration resets or sets to a hex value 0x1400.

We have read the datasheet and verified the voltages to be correct as follows:

AVDD : 6.73V

DVDD : 3.4V

GVDD : 10.96

En_GATE : High

PVDD : 24V

Can we get some help on what could be the reason for the problem we are facing?

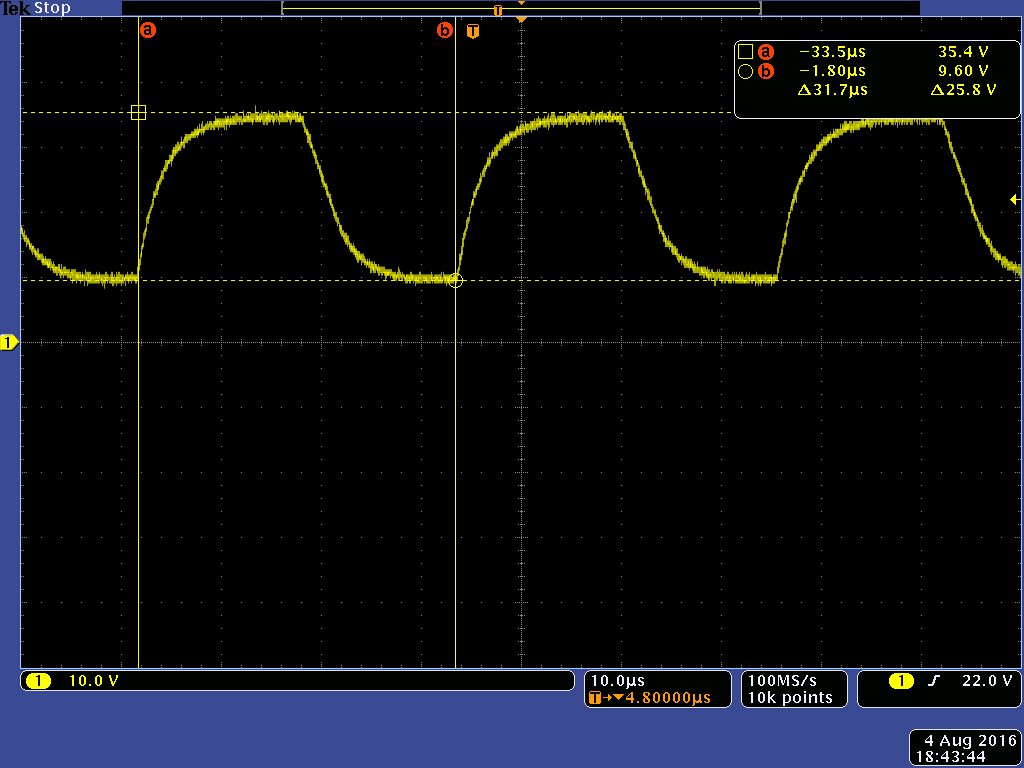

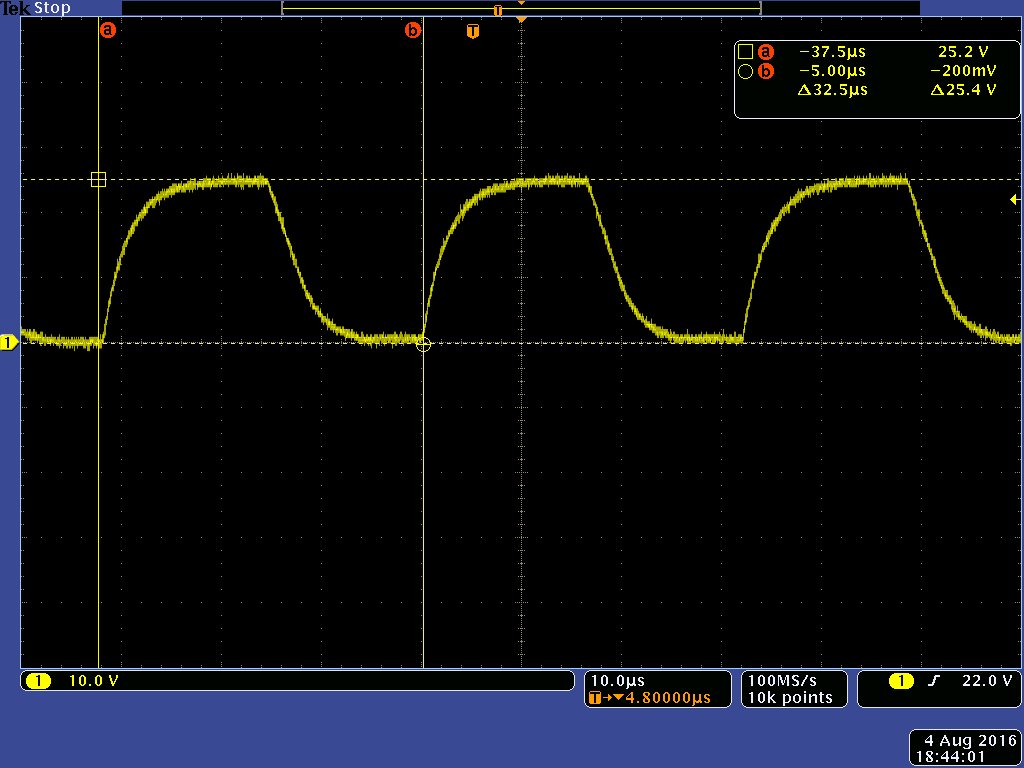

Moreover