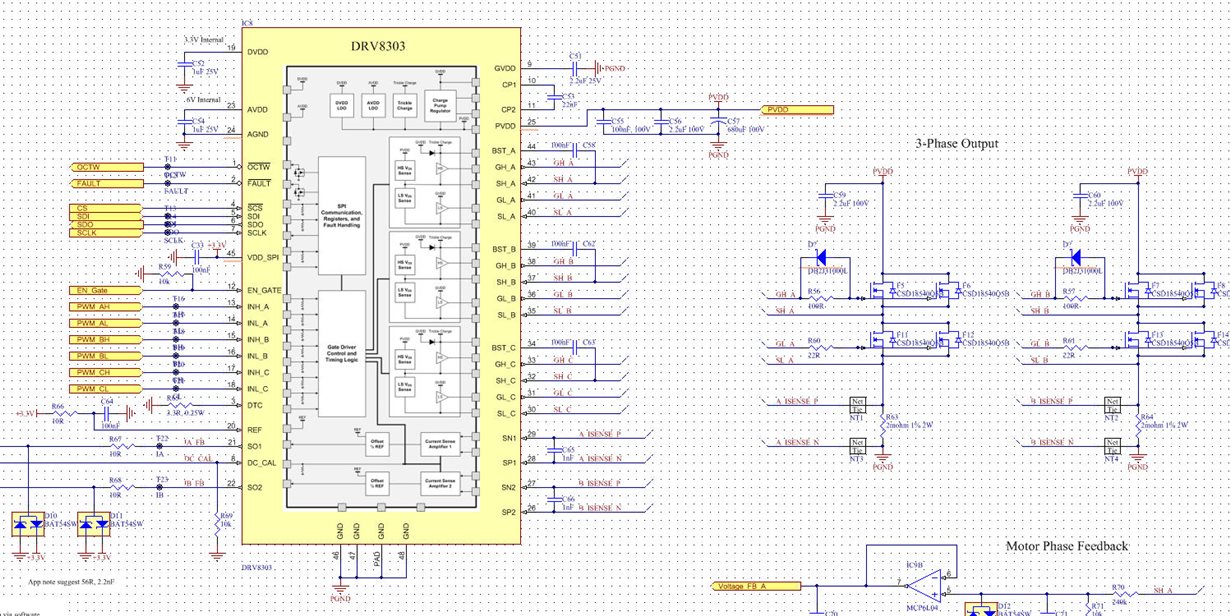

Other Parts Discussed in Thread: BOOSTXL-DRV8301, CSD18540Q5B, DRV8301, CSD19532Q5B

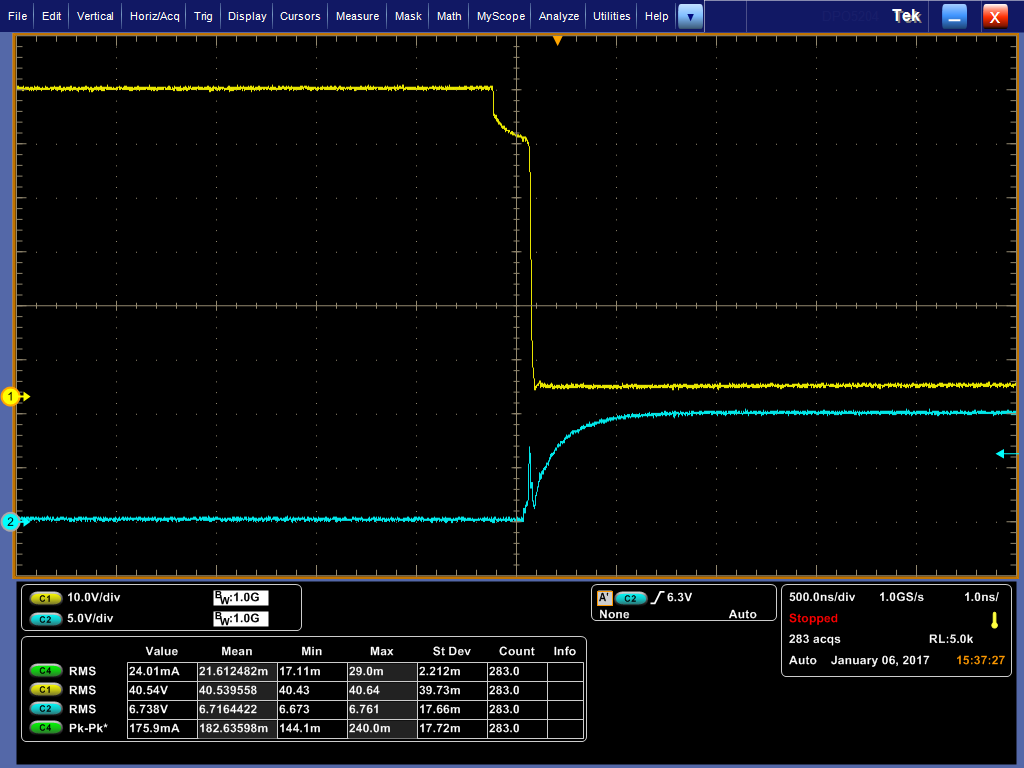

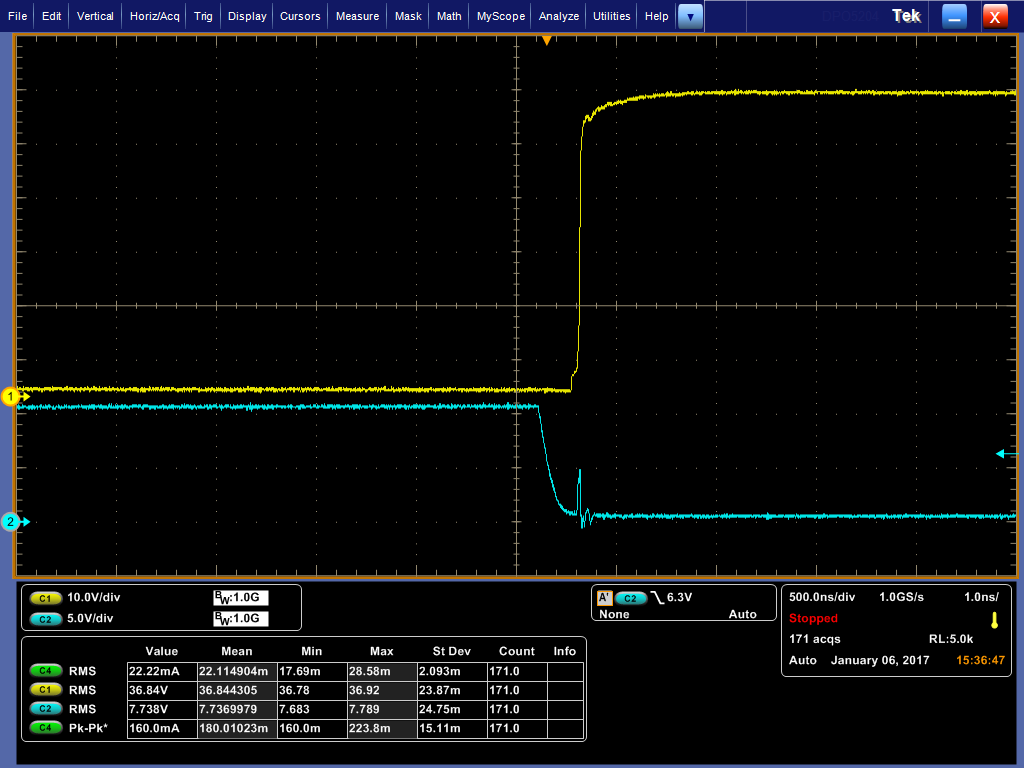

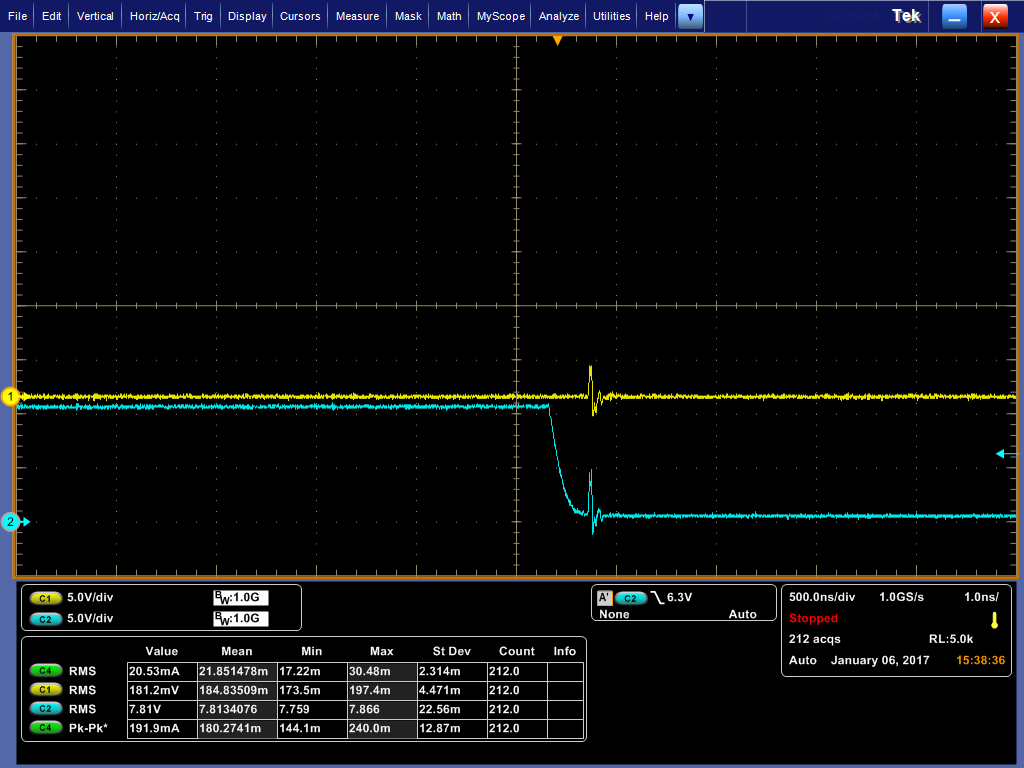

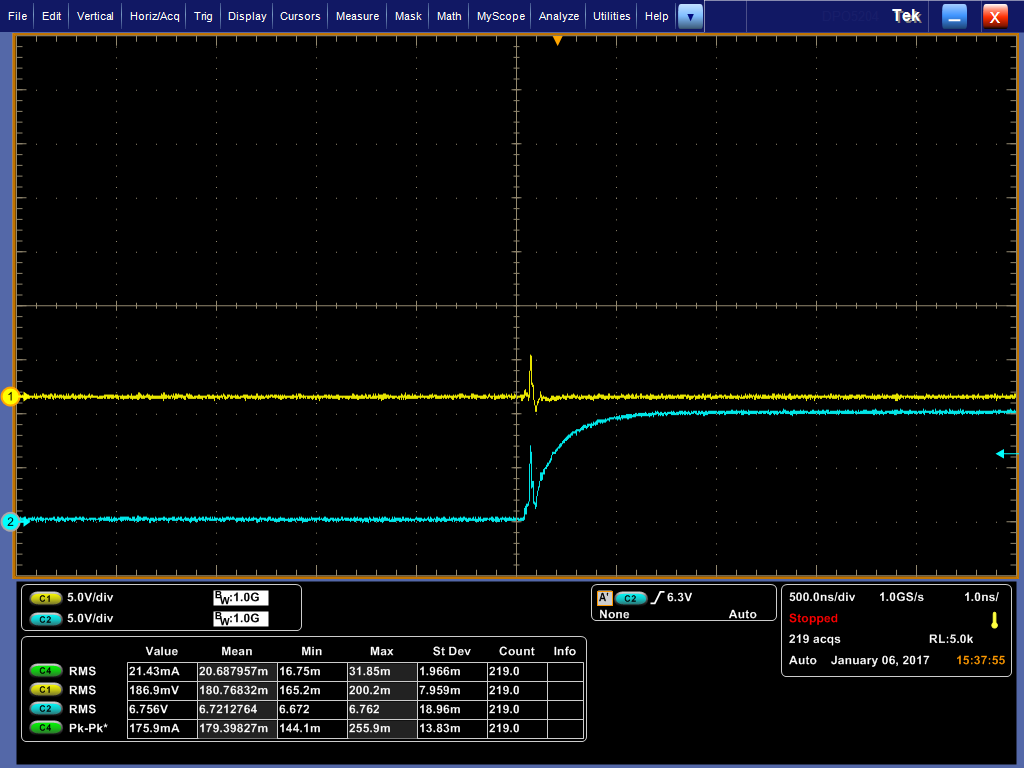

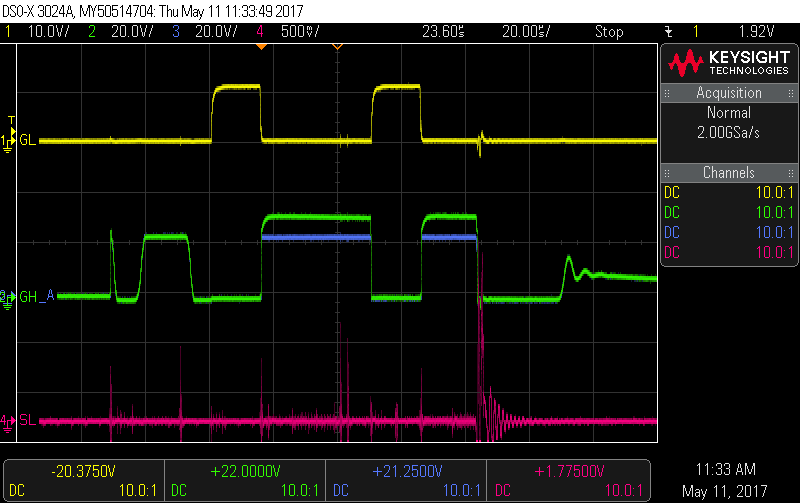

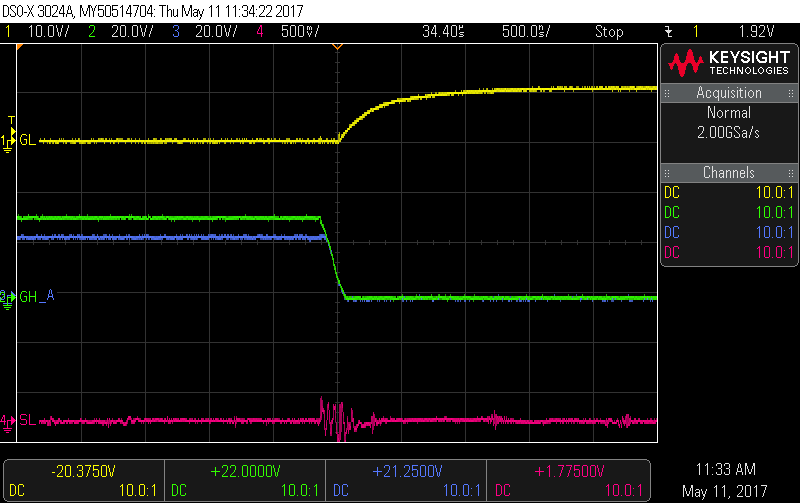

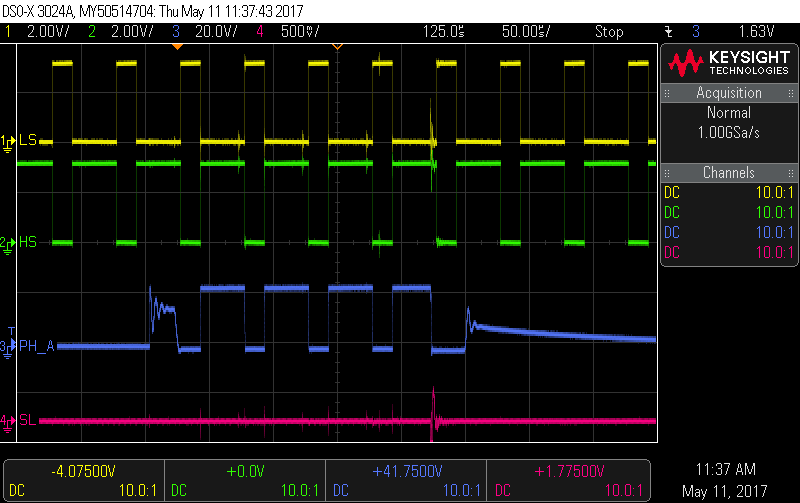

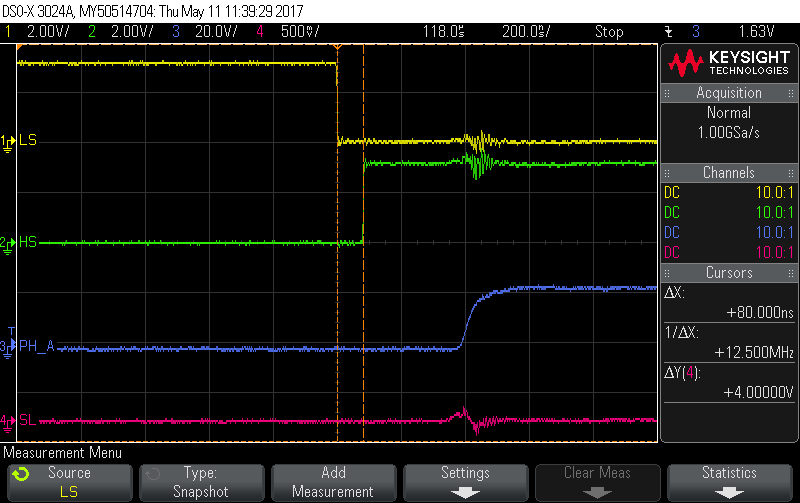

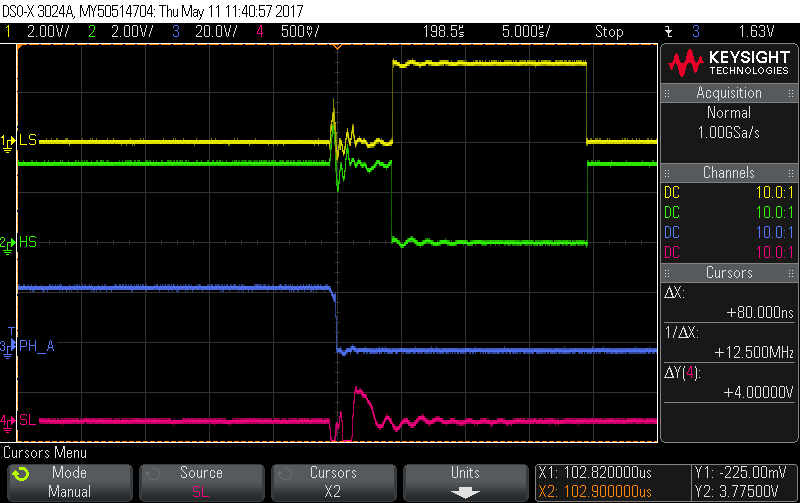

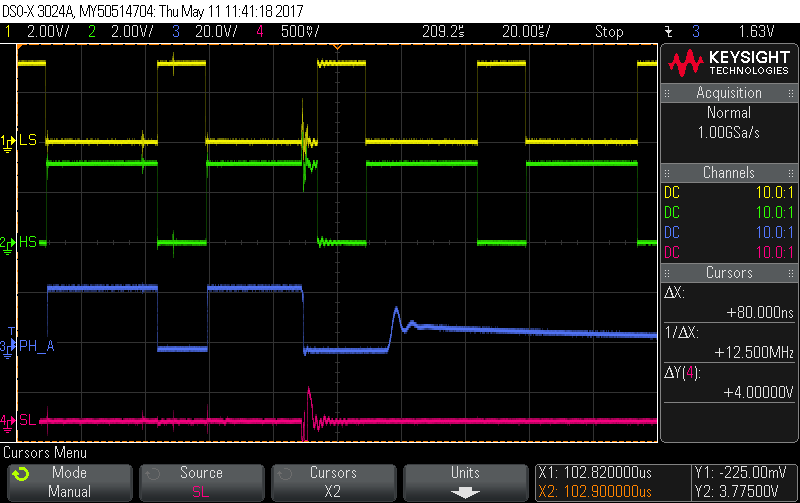

We are using theTMS320F28069MPZT and the DRV8303 and have a problem with the GLx (lower gate output drive) spiking up when there is a transition on the GHx signal (high side gate output) the result is high currents (3V/0.025 ohms = 120A!) flowing through. The Rsense in this circuit is 0.025ohms. Increasing the dead time has no effect on the GLx output drive spiking high. We had the boards x-rayed to confirm that the exposed pad of the DRV8303 was properly connected to the ground plane.

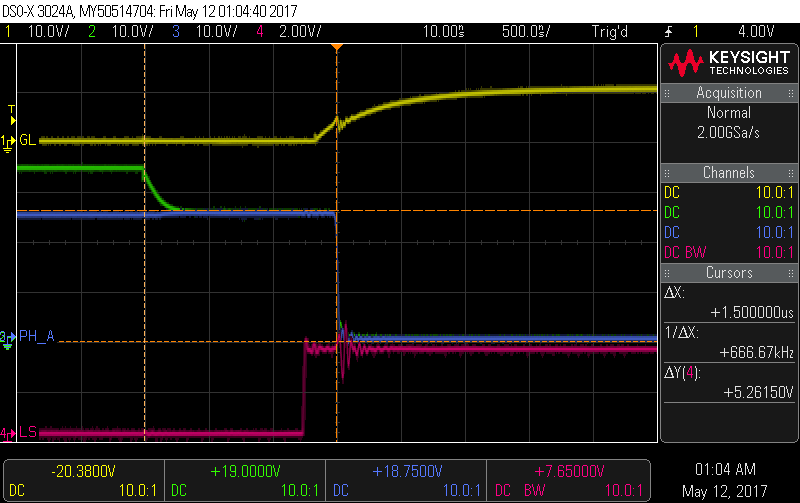

We then set up the BOOSTXL-DRV8301 board and it behaved similarly; high current spikes on the edges of the high side gate drive. We are very careful with our scope grounds and confirmed that what we are measuring is truly present.

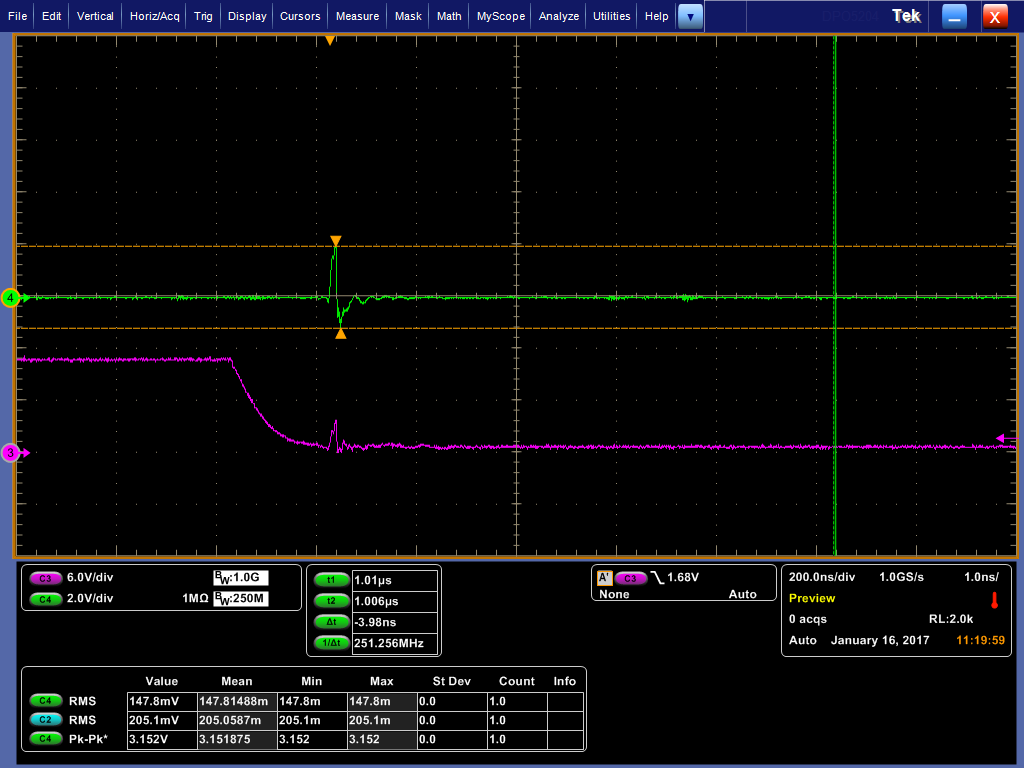

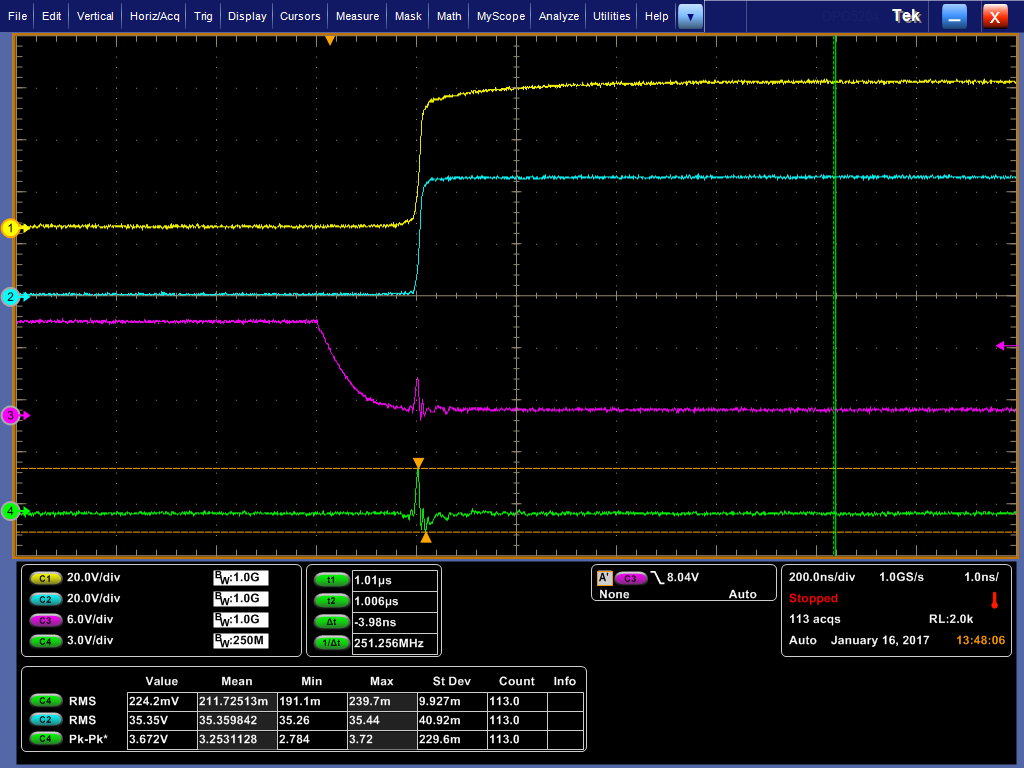

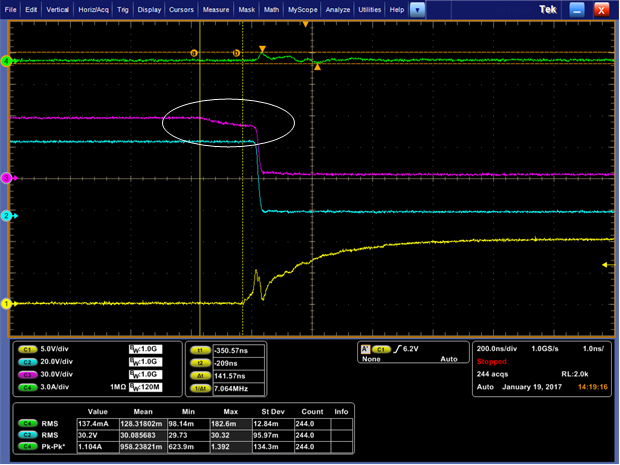

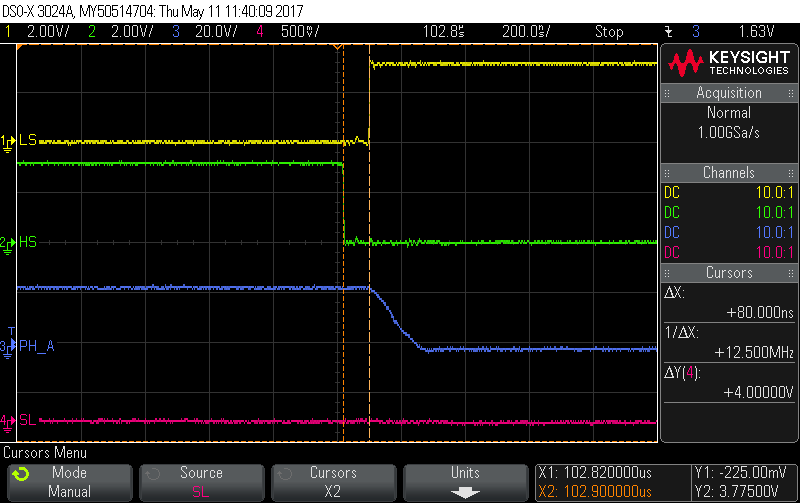

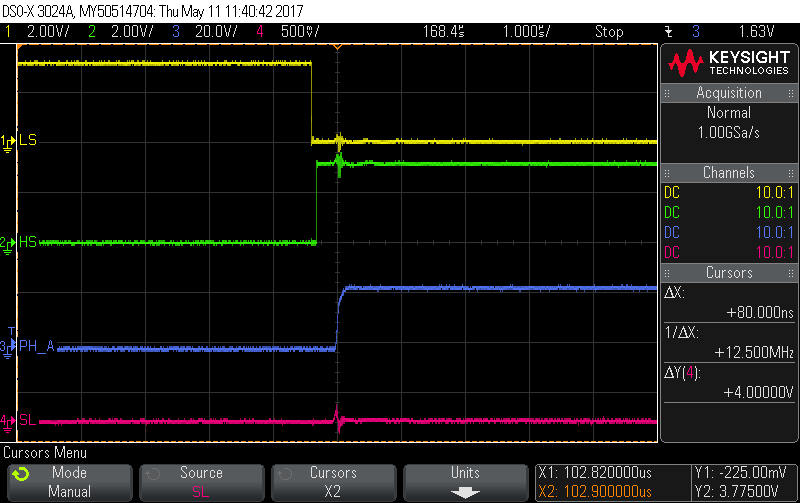

For the following images, the FOC software was set in the RS Recalibration mode for Motor Identification. The motor isn’t spinning. However when the motor is spinning, these spike are still present.

DRV8303 GH Falling and GL Rising

DRV8303 GH Rising and GL Falling

DRV8303 GL Falling and Voltage on RSense

DRV8303 GL Rising and Voltage on RSense