Hello,

As a learning exercise I am designing an audio DAC. I'm doing this in a modular way so as to be able to iterate on various stages, so each stage has headers for connecting to the next board. I've designed the first stage around the CP2615 which seems to work correctly. Now I am working on the DAC (I2S -> Analog), designed around the PCM5242 chip. This stage will output to the final stage, which will be the amplification stage.

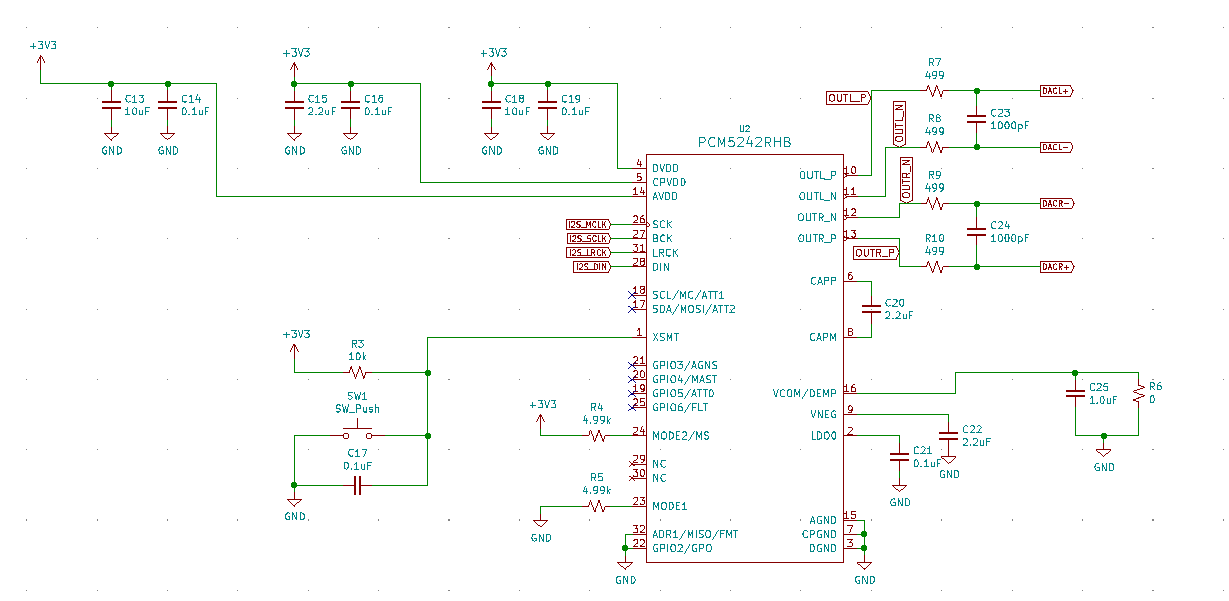

The relevant schematic portion is here, with some minor modifications (see below):

Notes/Changes:

- R4 is not populated, MODE2 is jumpered to ground so as to set HARDWARE mode

- R6 is not populated

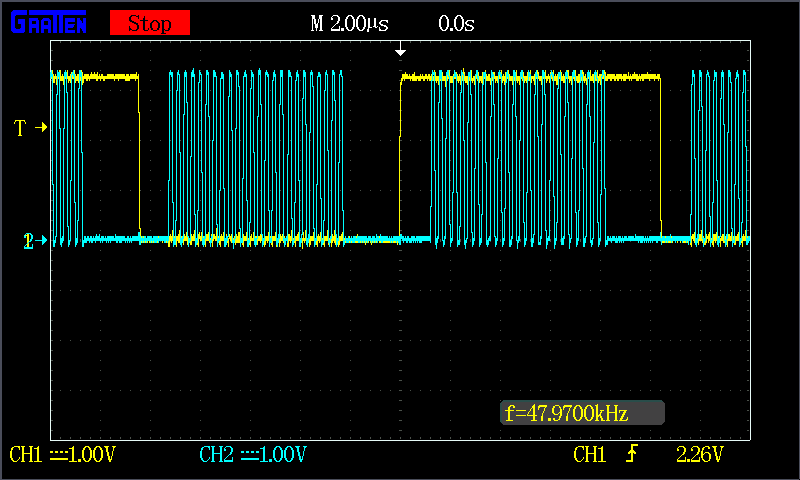

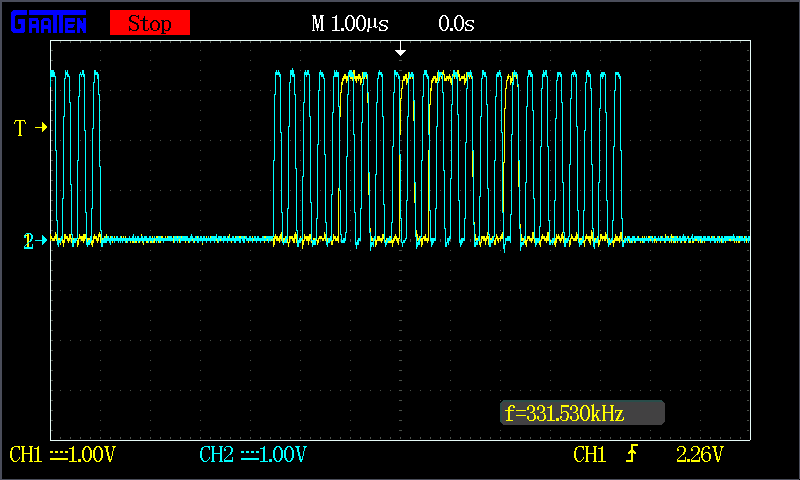

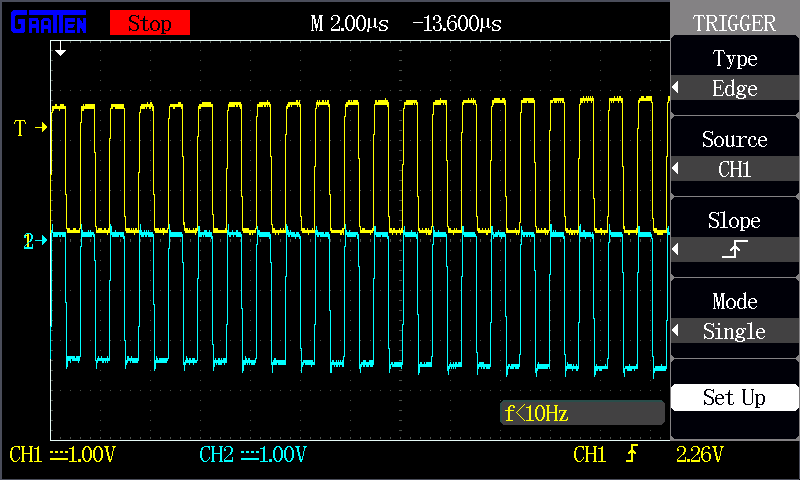

- I2S input signals @ 3.3V

- CAPP/CAPM appear to be working correctly

- VNEG is correctly creating -3.3V

- LDO0 is correctly creating 1.8V

- Input data format is 24-bit I2S

The issue: none of the output pins are showing any signal, and I'm not sure what to do to debug this. I've checked with a microscope that all of the connections look good -- what else might I try, or did I make a mistake on my schematic that might be causing this not to work as expected?

Thank you,

Jonathan