Hello,

On my TLV320AIC3204, I am using the primary audio port with BCLK (PIN 2) set as input and receiving a 128kHz 50% duty PWM from an MCU. In return, the WCLK (PIN 3) outputs an 8kHz 50% duty PWM along with 8-bit audio on DOUT (PIN 5) to that MCU.

Internally on the CODEC, I route MIC 1 (IN1L and CM1L) to the left MIC PGA channel like this:

P1_R52_0b01000000

P1_R54_0b01000000

The result is that the audio from my microphone is converted to an 8-bit digitized audio stream and that's perfect.

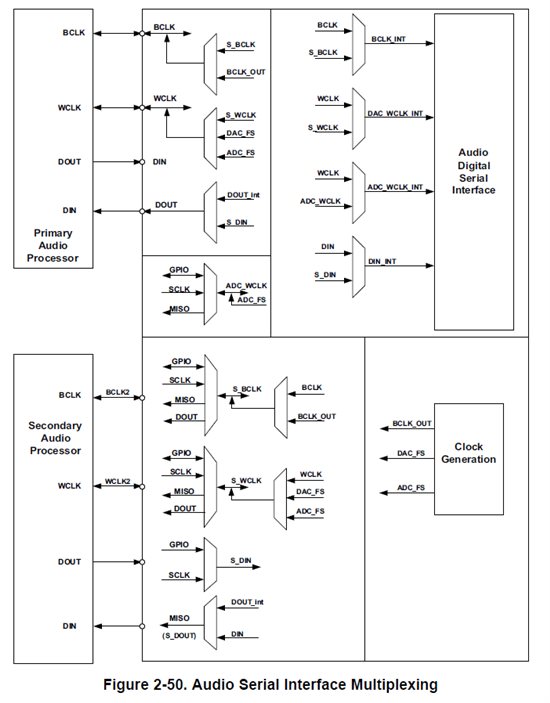

Now, the CODEC has a SECONDARY I2S port and it turns-out I have a second audio device. This device is generating both clocks and expects to receive digitized audio.

My MCU configures all CODEC registers through I2C, not SPI. I think I cannot use secondary I2S if I am using SPI. So this is not an issue.

IMPORTANT NOTE: I will be using only ONE audio device at a time. So on occasions, I will stream to DOUT 1, on other occasions, I will stream to DOUT 2, but never on both (not possible anyways I think).

I was thiking of using the following pins on the CODEC as my secondary I2S block:

SECONDARY BCLK (PIN 8)

SECONDARY WCLK (PIN 4)

SECONDARY DOUT (PIN 11)

In this case, both the S_BCLK and S_WCLK need to be set as input on the CODEC. S_BCLK will be receiving a 2.048MHz 50% duty PWM, S_WCLK will be receiving an 8kHz short-sync pulse and in return, I need S_DOUT to output that digitized audio bitstream to that secondary device's DIN.

Question 1: Which registers with which values do I need to set to configure this SECONDARY I2S port? I am going through the documentation and registers but I am not sure which registers to configure.

Question 2: Once I configure these registers, how do I tell the CODEC to internally route MIC 1's analog input so that it gets sent out on S_DOUT (PI 11) as opposed to DOUT (PIN 5)?

Basically, I want to mimic what I am doing on the PRIMARY port with Mic 1 but do it on the SECONDARY port with the only difference being that on the PRIMARY port, BCLK is an input and WCLK is an output and on the SECONDARY port, both clocks are inputs?

I need the exact registers and values please.

Thanks!