I'm using 2 src4382's in a design that for this version is only using the AES DIR and DIT as s/pdif through the src. I'm using an Atmel ATTiny44 as the controller. It is all working as it should as I used the EVAL board to learn how to set up the src4382. The problem I'm having and this is the show stopper is the behavior of the the Ratio Read registers 0x32 and 0x33. I am using a dual frequency programmable 3.3V MEMS oscillator, a Silicon Labs 502BBD-ADAF with freq 1 programmed to 24.5760mhz and freq 2 programmed to 22.5792mhz. I've verified the frequencies are accurate and programming PORT A and or B and probing the L/R clock shows the proper frequency (using a scope with frequency counting). I am using the MCLK (pin25) input for all clocks. for the 24.5760mhz clock I'm using P=2, J=2, and D=0 (Receiver PLL configuration registers 0x0F, 0x10, 0x11), and for the 22.5792mhz clock I'm using P=2, J=8, D=7075 (decimal). The whole system works well, locks to the incoming stream and properly encodes an s/pdif output. This has been verified at all frequencies with recording studio s/pdif equipped devices. IT works, passes audio and sounds great.

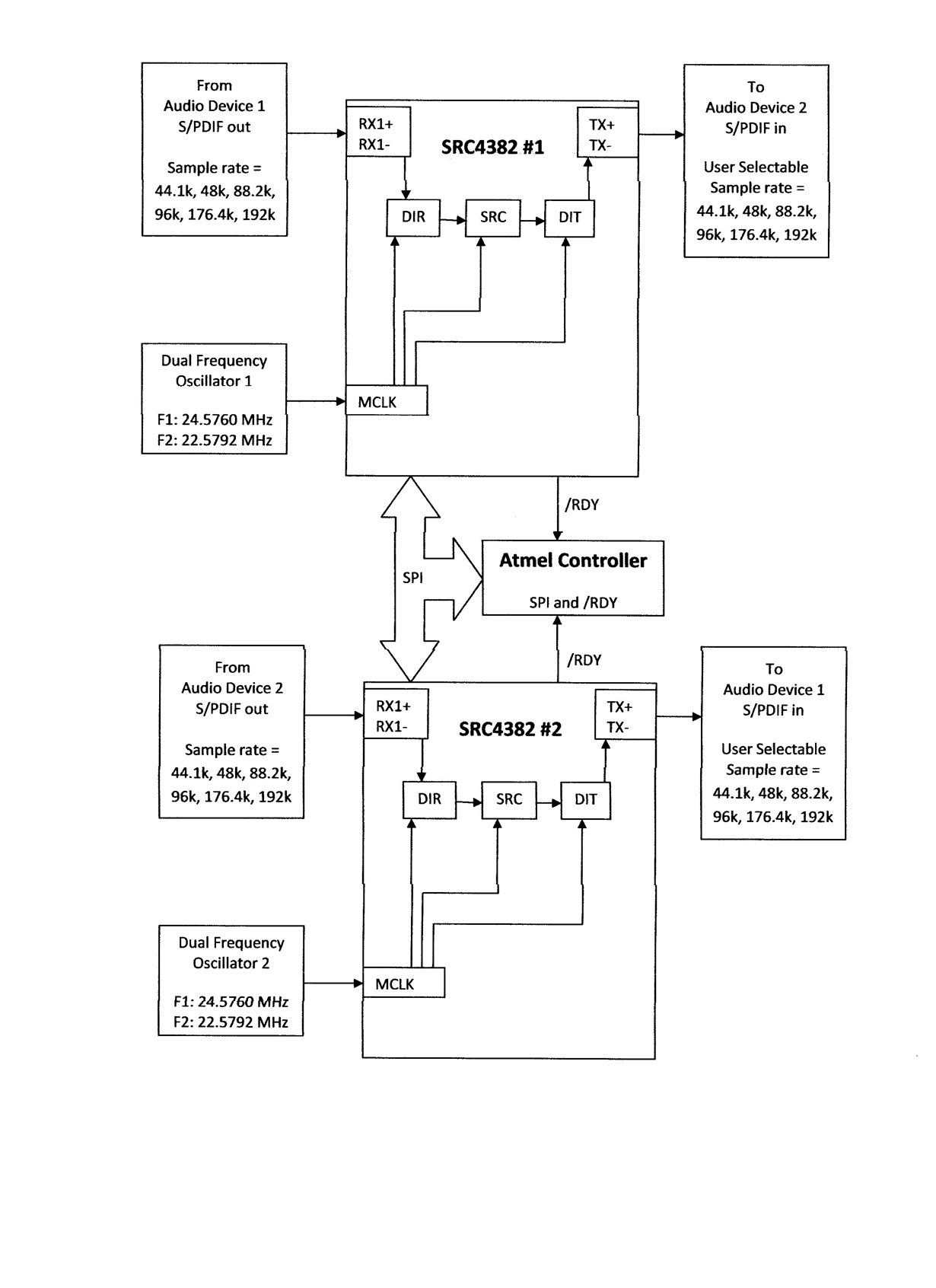

The 'showstopper' for this device with 2 src4382 is due to the requirement that either of the src's need to be made a 'master' or 'slave'. The idea is the an s/pdif output from the sending device enter's src1, is sr converted to a user selectable sr and goes out to a different s/pdif device's input. The output from that device's s/pdif stream then goes into src 2 (at the src framerate of src1) is converted to the src rate at the input of src1 and then sent to the originating device. This scenario is equivalent to an analog patch bay with an outboard device in the efx loop.

To accomplish this I need to know the I/O sample rate ratio. I have the /LOCK pin connected to a 2ma led (for lock indication) and also to a pin on the controller set up as an interrupt so it can interrogate the SR Ratio regs at the proper time. It all works as it is supposed to except the SR Ratio register is exhibiting some anomalies. When I have the MCLK pin receiving 24.5760mhz and the input is receiving 48khz, 96kz, or 192khz frame rates (pure integer ratio's : 1,2, or 4) register 0x32 reads back as all 1's, and register 0x33 reads back as all 0's. Decoded and bit shifted I get 0x1f (register 0x32) and 0x07 (register 0x33). I get the same behavior if MCLK is receiving 22.5792mhz and the receiver input is getting 44.1khz, 88.2khz, and 176.4khz frame rates (again pure integer ratios). However it all works like it's supposed to when I have the MCLK pin receiving 24.5760mhz and the receiver input is getting 44.1khz, 88.2khz, and 176.4khz frame rates and conversely with MCLK inputting 22.5792mhz and the receiver getting 48khz, 96khz, and 192khz frame rates. I get the ratios reported as they should be.

Obviously, if I can't know what the ratio is I can't know the proper divisor to use to set up the 'slave' src to mirror the 'master' src. I've tried everything I can think of and have looked through all the src4382 and src4392 threads relating to the ratio registers and tried those remedies also. I have not had any joy up to now.

At this point any help or knowledge of what I may be doing wrong or misinterpreting would be most welcome. Failing that, I would have to assume that this may be a bug in the silicon on the version I'm using? The part number stamped on the package is: SRC4382I , next line: 36C0GTT.