Hi,

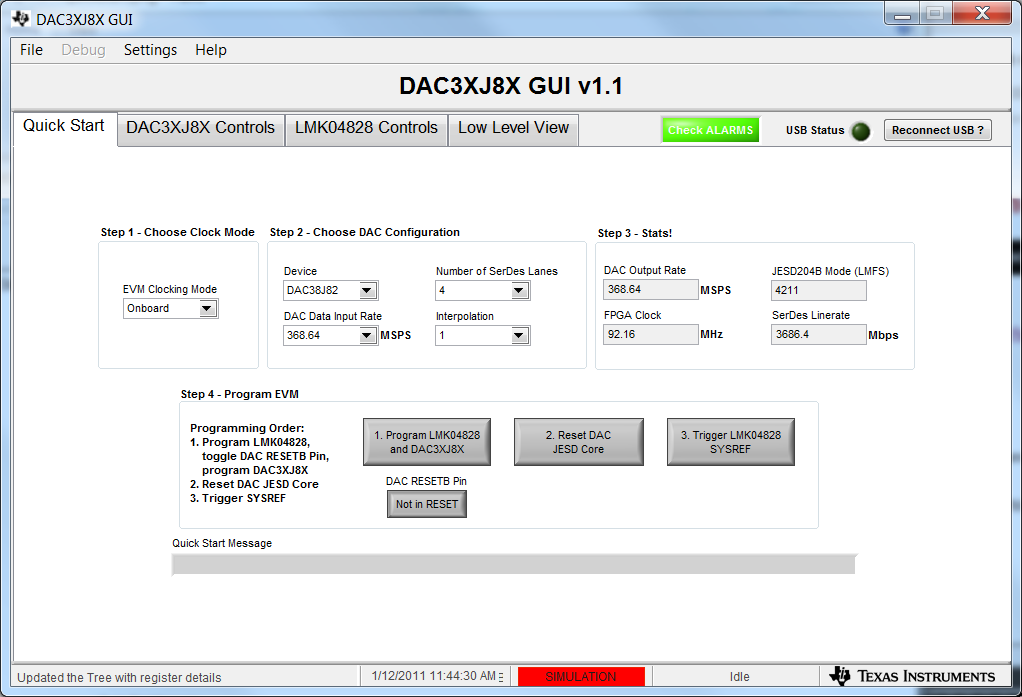

I am using the DAC3XJ8X EVM with Xilinx FPGA with FMC interface.

From DAC3XJ8X EVM GUI v1.0, there is a setting of "SERDES and Lane Configuration", there is a parameter of "Buswidth", it looks it can only be 16 or 20bit.

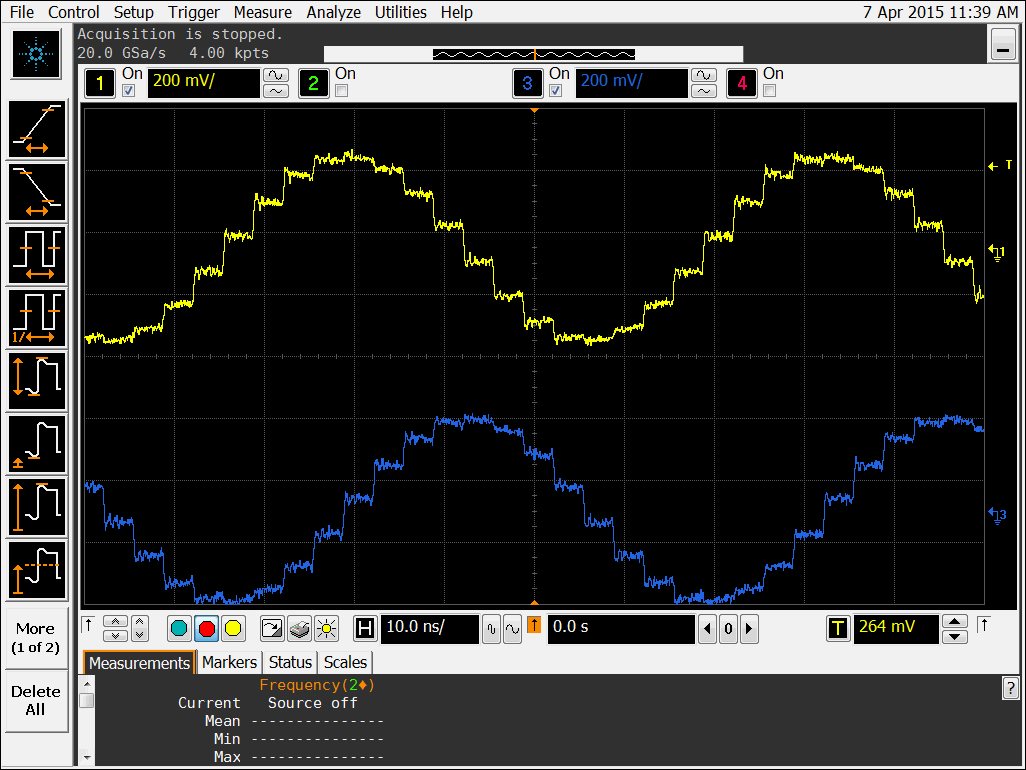

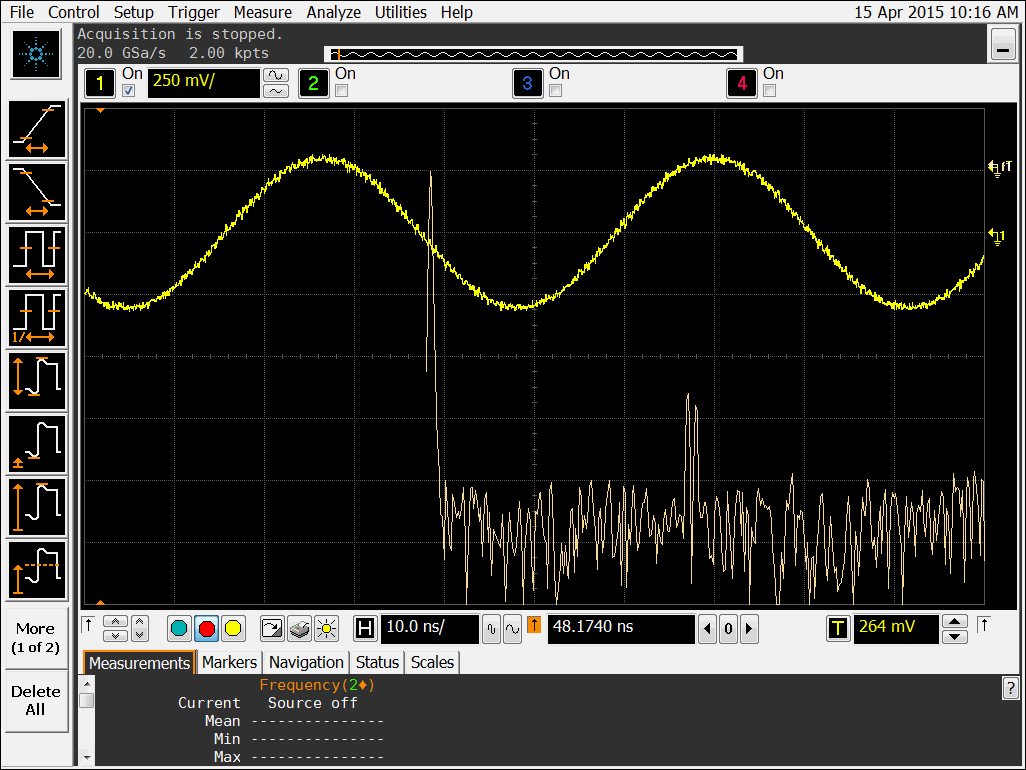

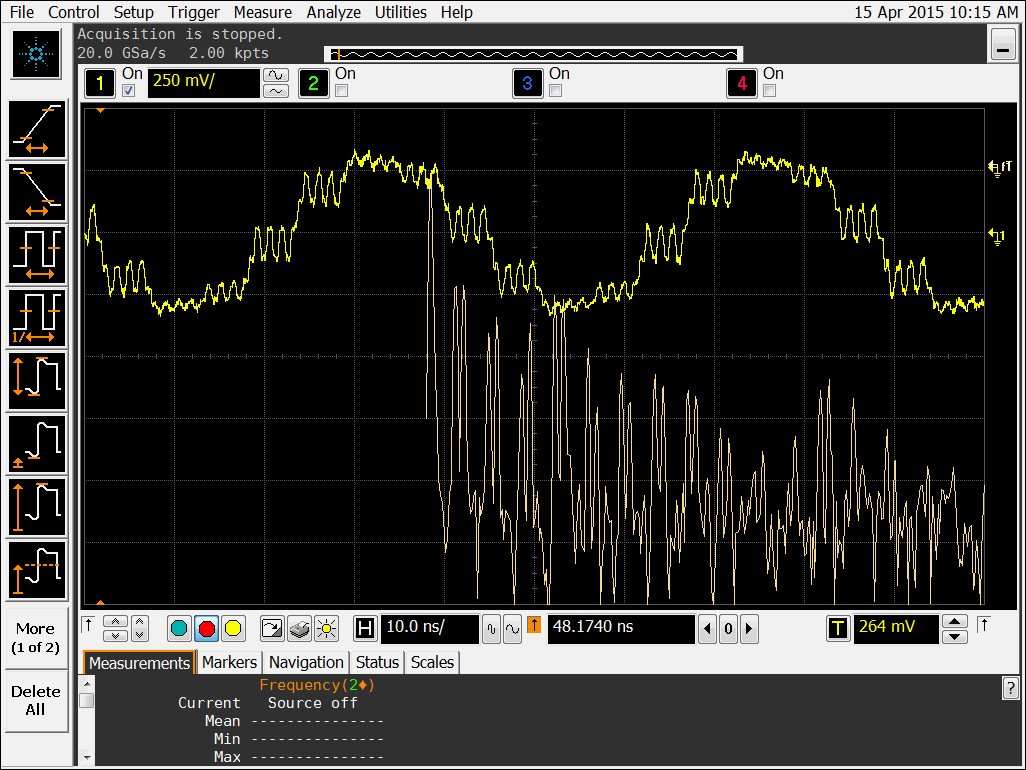

but my FPGA design requires JESD204B core to have 32bit in and SERESE buswidth = 40bit, so when I look at the DAC output, it looks only half of the samples are sent out, and the other half samples can not be seen from the DAC output.

my setting is LMFKS = 4 2 1 20 1. so lane0 and 1,

lane0 <= { tp_dac_i[0][15:8], tp_dac_i[1][15:8], tp_dac_i[2][15:8], tp_dac_i[3][15:8] } ;

lane1 <= { tp_dac_i[0][7:0], tp_dac_i[1][7:0], tp_dac_i[2][7:0], tp_dac_i[3][7:0] } ;

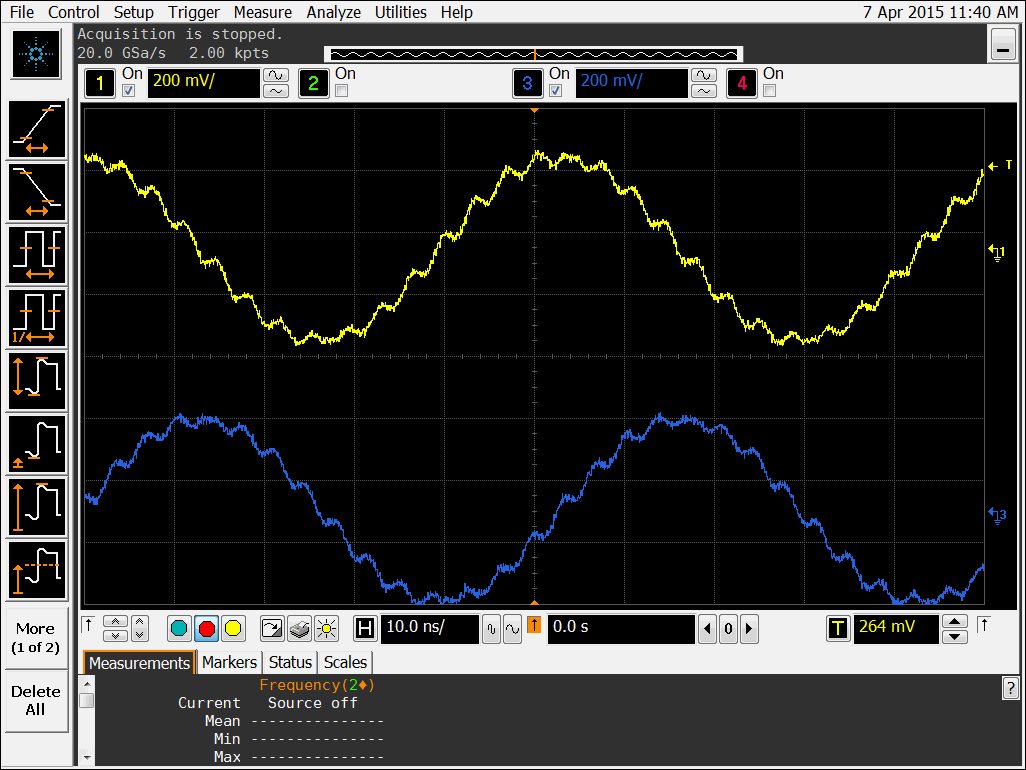

but from the output, it looks only tp_dac_i[0] and tp_dac_i[2] are seen.

is this related to buswidth ?