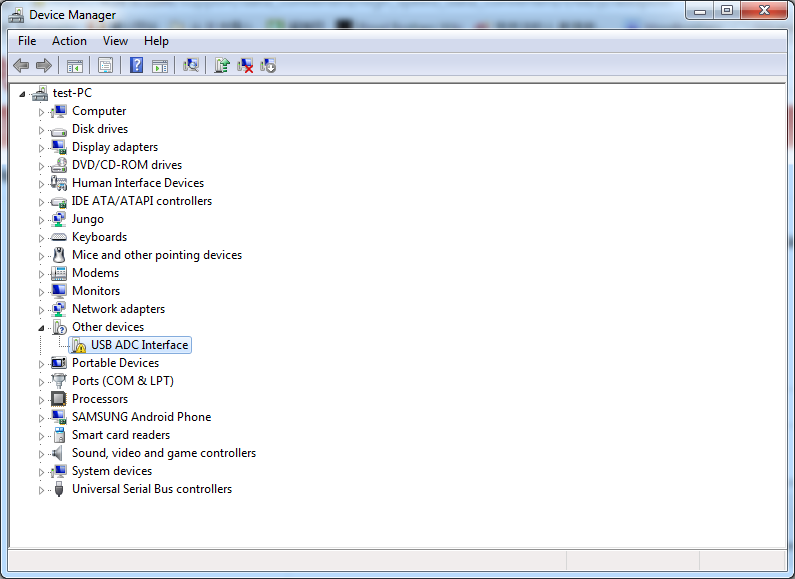

Hi, does anyone know how to use ADC SPI interface on windows 7 64 bits to initialize the ADS5282EVM? I spend two days on how to install the driver for this evm board, searched over this website and read all post related to ADC SPI interface and adc. However, the driver for this ADC board cannot install. I also download the new driver for windows 7 from Future Technology website (because this adc board used FT245BL USB chip), but the computer cannot find any driver for this board as well. This problem is showing below.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.