Hi!

I’m using the TSW54J60 (Rev B) for the feedback of a large bandwidth DPD system(Tx=TSW38J84,FPGA=VC707). I’m using discrete multitone signals with up to 200MHz bandwidth. I’m locating the IF at fs/4 (fs=8x122.88=983.04MHz) to get the maximum bandwidth out of the device (bandwidth of approx. 4x122.88= 491.52MHz).

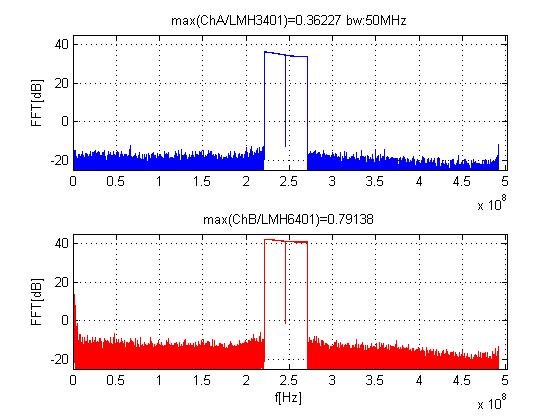

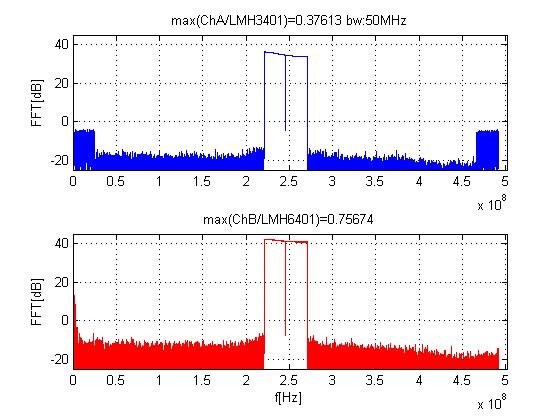

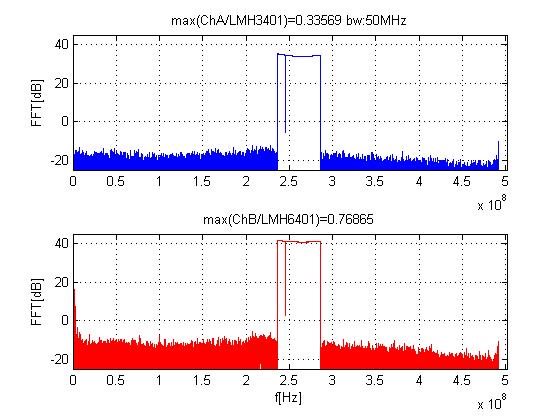

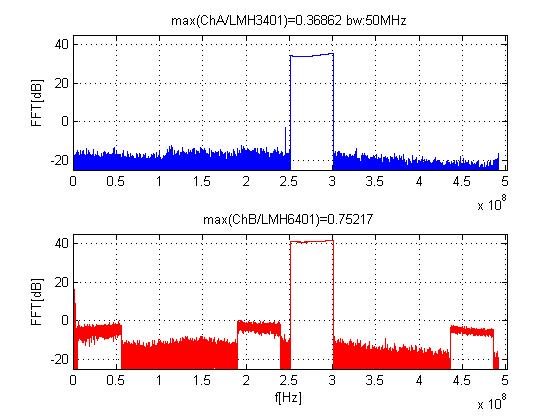

The problem is now that the interleaving correction does not work stable for signals located at IF=fs/4. The inband noise jumps (randomly) and is not constantly low as I would expect. I also tried to shift the signal slightly away from fs/4 which results in much better performance. But I still see sometimes the IL spurs...

For example: For a 50MHz bandwidth DMT signal I have seen better than 50dBc SNR. When the IL correction fails the SNR drops below 40dBc.

Another problem is that I don’t get any tone at fs/4. It’s almost cancel out by the ADC. Is this a normal behavior of this ADC? I cannot explain how it is possible that the fs/4 tone can be canceled out???

I have done a lot of test also with your provided config files but without success…

Using analog/digital reset does not lead to better results.

Have you ever seen such behavior on the ADS54J60 / TSW54J60??

Have you ever tried the TSW54J60 on the VC707 (FMC2 J37)??

How can I get the ADC interleaving correction stable?

Why (or better how) does the ADC kill the tone on fs/4 (2x122.88MHz)?

The JESD is working fine and I use the 4-Lane 8224 Mode with Scrambling enabled. I almost use 1dB fullscale of the ADC.

I appreciate any answere/help!!

Best regards!

Martin

Some off topic question/hint: The "Scrambling EN" checkbox of the ADS54JXX GUI (v1.5) does not work. Since it happens nothing (the GUi doesn't send something) when I press it, I think its just the checkbox without any connection in the background... I had the same problem with the previous GUI version. Maybe its again a problem of my PC,... but its just a checkbox and all others do work,...