Hi team,

My customer is going to connect ADS54J60 to KC705, and has following two questions.

Please let me know the answers. I could not find the answers in the datasheet and E2E.

(1) How can I set ADS54J60 to output through only channel B.

KC705 connects to only channel B of ADS54J60.

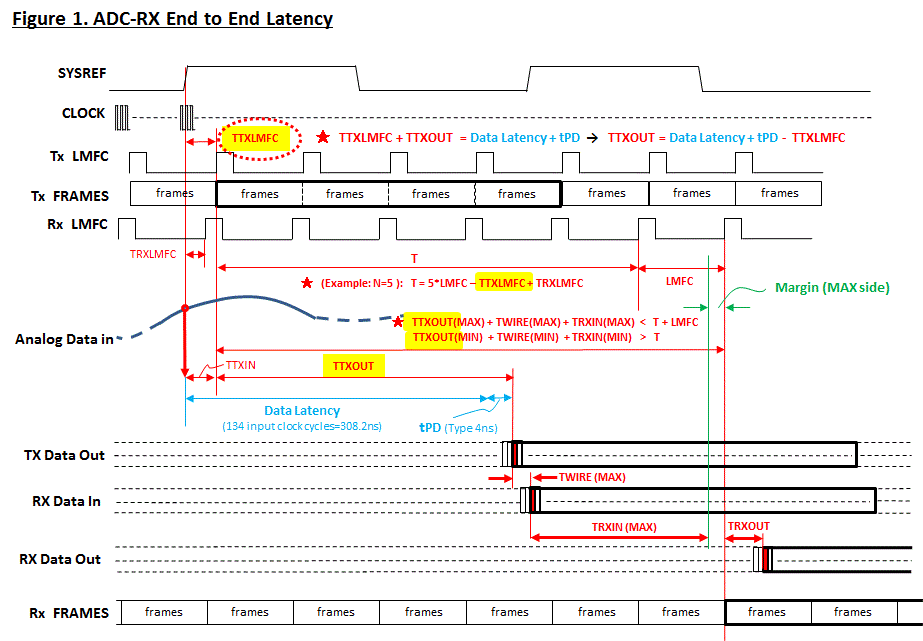

(2) Please let me know ADS54J60 TTXLFMC value and TXOUT value.

I need these values to calculate end-to-end latency.

As to TTXLFMC and TXOUT, please refer to page.60 of following Xilinx LogiCORE IP Product Guide:

www.xilinx.com/.../pg066-jesd204.pdf

JESD Parameters are as follows:

・LMFS : 4211

・JESD PLL Mode : 40x

・f_SYSREF : 3.125MHz

・k : 32

・f_LMFC : 12.5MHz

・Decimation filter: none

Best regards,

Fumio Nakano

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.