Other Parts Discussed in Thread: ADC12DJ3200, TSW14J57EVM,

Hi TI team,

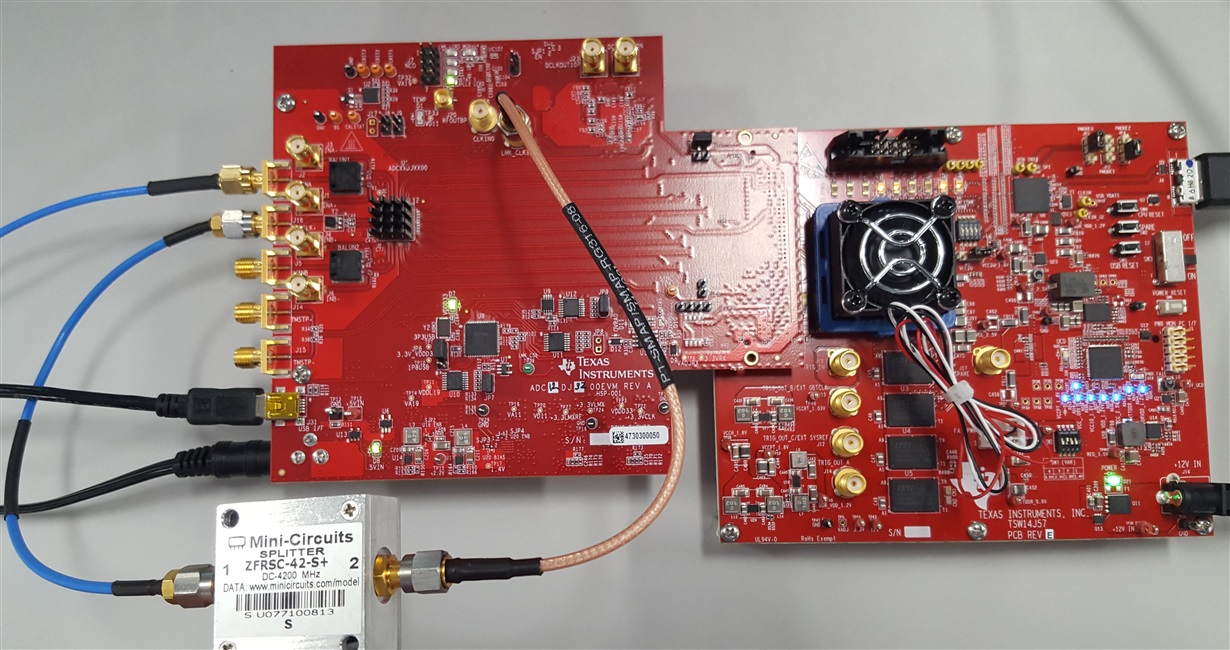

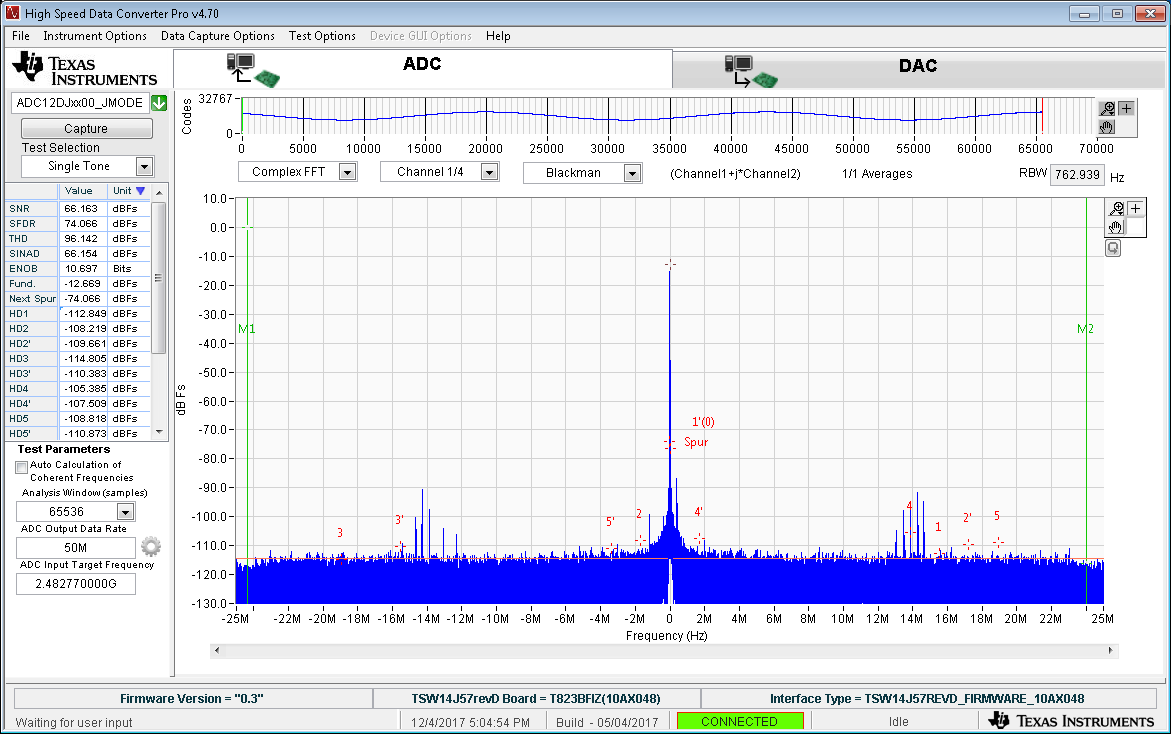

When I am evaluating ADC12DJ3200 EVM. I configured for 2700 Msps with JMODE16 it working fine. But when I configured to "800" MSPs with JMODE 16 and similarly configured for JMODE0. In both cases it throwing error. I verified as per error thrown on hardware D4 is not blinking and D3 glowing up. I am thinking like clock is not going From ADC board to TSW FPGA board.but as per data sheet it should support 800 Msps also. may I know the what could be the reason for this problem.? Is this due to hardware limitation or we are missing any config settings.